Знакомство с принципом работы мультиплексора и демультиплексора; получение навыков работы по определению временных диаграмм и составлению таблиц соответствия

ЛАБОРАТОРНАЯ РАБОТА №1

МУЛЬТИПЛЕКСОРЫ И ДЕМУЛЬТИПЛЕКСОРЫ

Цель работы: знакомство с принципом работы мультиплексора и демультиплексора; получение навыков работы по определению временных диаграмм и составлению таблиц соответствия.

ОСНОВНЫЕ ПОНЯТИЯ

Мультиплексоры и демультиплексоры – логические схемы, осуществляющие многопозиционную коммутацию цифровых сигналов.

Мультиплексор – логическая схема, осуществляющая коммутацию цифровых сигналов с одного входа на один из нескольких выходов, в зависимости от состояния адресных входов (кода адреса).

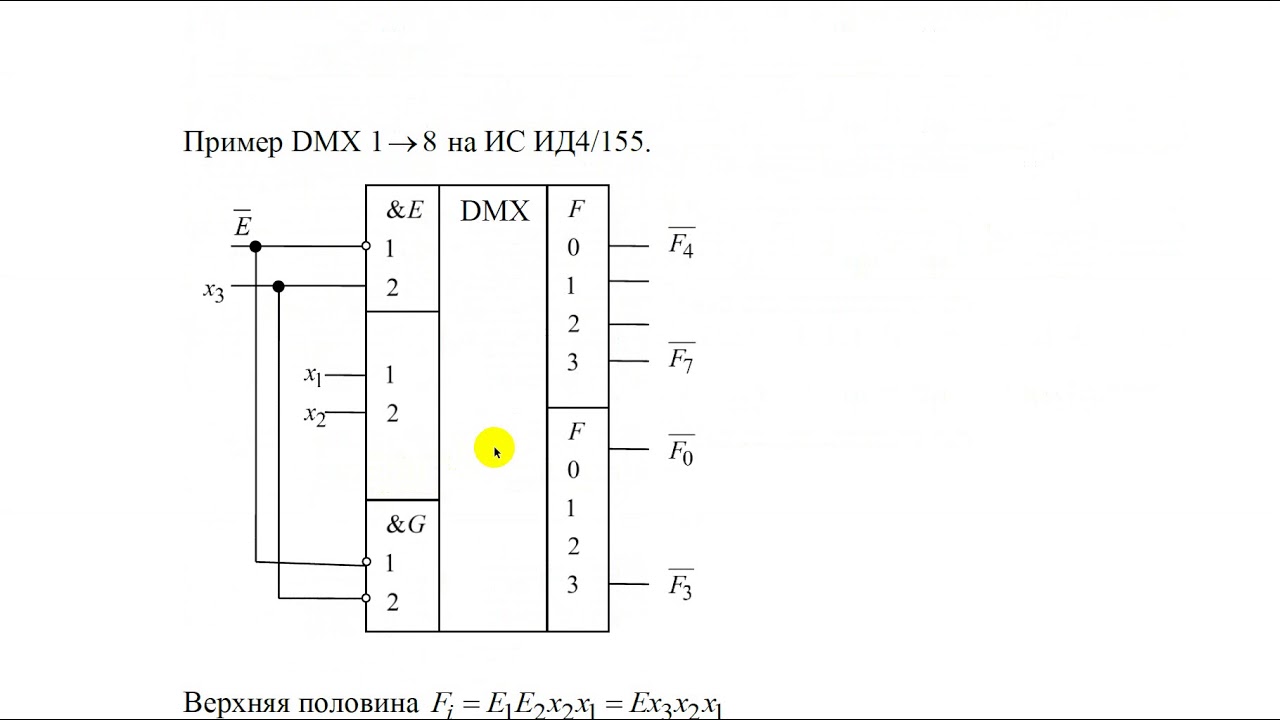

Демультиплексор – логическая схема, осуществляющая коммутацию цифровых сигналов с одного из нескольких входов на один выход, в зависимости от состояния адресных входов (кода адреса).

Входы:

информационные; адресные и разрешающие (стробирующие) (служебные).

Выходы: информационные (прямые и/или инверсные).

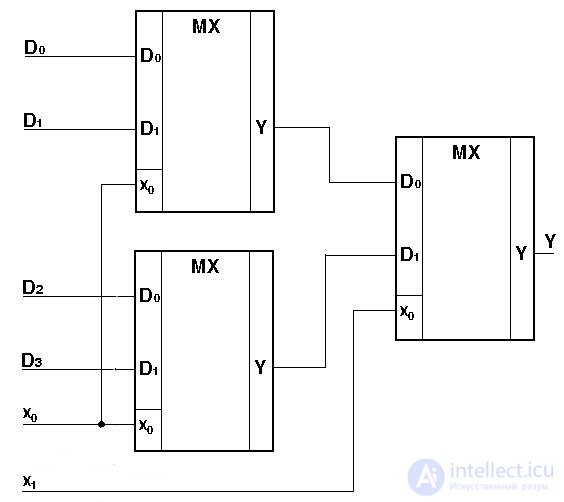

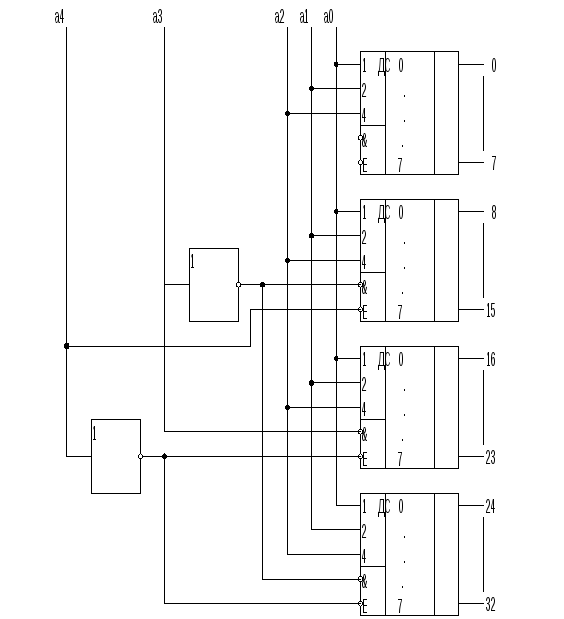

Мультиплексоры могут быть объединены для наращивания разрядности. 2 способа: в пирамидальную схему либо последовательным соединением разрешающих входов и внешних логических элементов. Так же могут быть объединены демультиплексоры.

ИСХОДНЫЕ ДАННЫЕ

Мультиплексор:

1) 0110

2) 10010011

Демультиплексор:

1) 1000

2) 10010001

РЕЗУЛЬТАТЫ ПРОВЕДЕНИЯ РАБОТЫ

Таблицы соответствия:

Таблица 1 – четырехразрядный мультиплексор:

Двоичный код числа на входе мультиплексора | № тактового импульса | Адресный вход Х1 | Адресный вход Х2 | Выход У | |||

D0 | D1 | D2 | D3 | ||||

0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 |

0 | 1 | 1 | 0 | 2 | 0 | 1 | 1 |

1 | 1 | 0 | 3 | 1 | 0 | 1 | |

0 | 1 | 1 | 0 | 4 | 1 | 1 | 0 |

Таблица 2 – восьмиразрядный мультиплексор:

Двоичный код числа на входе мультиплексора | № тактового импульса | Адресный вход Х1 | Адресный вход Х2 | Адресный вход Х3 | Выход У | |||||||

D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | |||||

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | |

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 2 | 0 | 0 | 1 | 0 |

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 3 | 0 | 1 | 0 | 0 |

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 4 | 0 | 1 | 1 | 1 |

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 5 | 1 | 0 | 0 | 0 |

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 6 | 1 | 0 | 1 | 0 |

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 7 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 8 | 1 | 1 | 1 | 1 |

Таблица 3 – четырехразрядный демультиплексор:

Двоичный код числа на входе мультиплексора | № тактового импульса | Адресный вход Х1 | Адресный вход Х2 | Выходы | |||

У0 | У1 | У2 | У3 | ||||

1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

0 | 2 | 0 | 1 | 1 | 1 | 1 | 1 |

0 | 3 | 1 | 0 | 1 | 1 | 1 | 1 |

0 | 4 | 1 | 1 | 1 | 1 | 1 | 1 |

Таблица 4 – восьмиразрядный демультиплексор:

Двоичный код числа на входе мультиплексора | № тактового импульса | Адресный вход Х1 | Адресный вход Х2 | Адресный вход Х3 | Выходы |

У0 У1 У2 У3 У4 У5 У6 У7 | |||||

1 | 1 | 0 | 0 | 0 | 0 1 1 1 1 1 1 1 |

0 | 2 | 0 | 0 | 1 | 1 1 1 1 1 1 1 1 |

0 | 3 | 0 | 1 | 0 | 1 1 1 1 1 1 1 1 |

1 | 4 | 0 | 1 | 1 | 1 1 1 0 1 1 1 1 |

0 | 5 | 1 | 0 | 0 | 1 1 1 1 1 1 1 1 |

0 | 6 | 1 | 0 | 1 | 1 1 1 1 1 1 1 1 |

7 | 1 | 1 | 0 | 1 1 1 1 1 1 1 1 | |

1 | 8 | 1 | 1 | 1 | 1 1 1 1 1 1 1 0 |

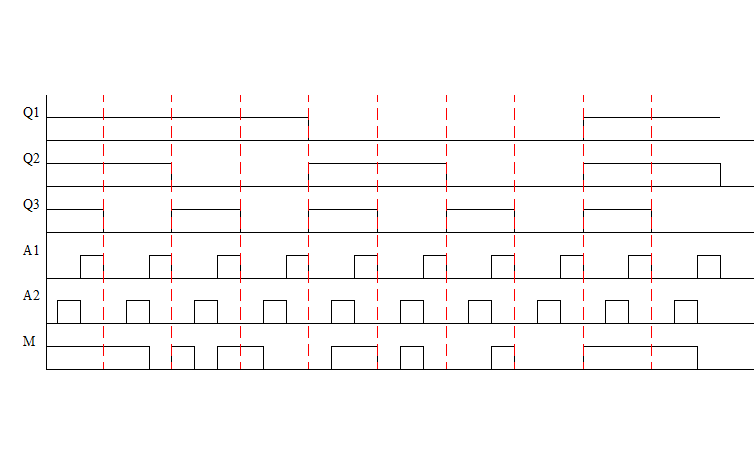

Временные диаграммы:

Диаграмма 1 – четырехразрядный мультиплексор:

Диаграмма 2 – восьмиразрядный мультиплексор:

Диаграмма 3 – четырехразрядный демультиплексор:

Диаграмма 4 – восьмиразрядный демультиплексор:

Вывод. В

процессе выполнения работы мы на практике познакомились с работой

мультиплексора и демультиплексора, а также получили практические навыки по

составлению временных диаграмм и таблиц соответствия.

В

процессе выполнения работы мы на практике познакомились с работой

мультиплексора и демультиплексора, а также получили практические навыки по

составлению временных диаграмм и таблиц соответствия.

4.3 Выбор и обоснование мультиплексора. Управление рабочими механизмами

Похожие главы из других работ:

Автоматизация процесса измельчения зерна

2. Выбор и обоснование датчиков

Необходимо стабилизировать частоту вращения рабочего органа вальца. Диапазон регулирования y0 = 250 ± 5 об/мин. Согласно заданию у 0 =250 об/мин (середина диапазона). Подбираем датчики с диапазоном 200…300об/мин и классом точности 1,0…

Выбор материалов на пальто женское демисезонное из натурального меха

1.3 Выбор и обоснование модели

Каждый век приносил глобальные перемены в одежде. Ясно, что не станет исключением и нынешний. Сейчас на первый взгляд кажется, что революций в моде нет: все тот же крой, все те же вещи. Но мода не стоит на месте. Она активно экспериментирует…

Она активно экспериментирует…

Комплекс по производству товарного кубовидного щебня производительностью 100 т/ч с разработкой дробилки

2.1 Обоснование и выбор бил

Можно выделить несколько видов бил для измельчения нерудных строительных материалов. Для измельчения гравия применяются била изображенных на рисунке 2.1 Рисунок 2.1 -Схема молотков с рабочими поверхностями. Крупность исходного материала…

Конструкторско-технологическая подготовка мелкосерийного производства валов агрегатов авиационных двигателей на специализированном участке

1.2.1 Выбор и обоснование параметров

Выбор параметров двигателя осуществляется в соответствии с рекомендациями, изложенными в методическом пособии[1]. В зависимости от назначения и условий, при которых рассчитывается двигатель, выбираются параметры узлов (ВХ, K, кс, г, т*, рн…

Подбор гидродвигателя к станку модели ЗУ131М

3. Выбор и обоснование номинального давления в гидросистеме привода, выбор рабочей жидкости

Исходя из паспорта станка, выбираем в качестве рабочей жидкости масло “Турбинное – Т22” ГОСТ32-74. Рабочую жидкость заливают перед пуском станка в резервуар 1 через заливную горловину 8 до уровня верхнего маслоуказателя 9…

Приводной газотурбинный двигатель для передвижной электростанции

1.1 Выбор и обоснование параметров

Температура газа перед турбиной Увеличение температуры газа перед турбиной Тг* позволяет значительно увеличить удельную мощность двигателя и, следовательно, уменьшить габаритные размеры и массу двигателя…

Прогрессивные технологические процессы на основе современных достижений науки и техники

3.2.1 Выбор и обоснование баз

От правильного выбора технологических баз во многом зависит качество обработки детали. Здесь следует, прежде всего, стремиться к соблюдению двух условий: 1) Совмещение баз, т.е. совмещение технологических баз с конструкторскими…

Проектирование участка механического цеха для обработки детали трактора – шестерня

2.5 Выбор и обоснование технологических баз

Под базированием заготовки в приспособлении понимают ее ориентацию относительно режущего инструмента или неподвижных частей станка. Базами называются исходные поверхности, линии или точки…

Базами называются исходные поверхности, линии или точки…

Проектирование участка механического цеха для обработки детали-представителя “Стакан подшипника”

2.5 Выбор и обоснование технологических баз

Базами называют исходные поверхности, линии или точки, определяющие положение заготовки в процессе обработки её на станке. Число и расположение базирующих поверхностей должно быть выбрано так…

Разработка технологического процесса изготовления детали “Основа излучателя”

3. Обоснование и выбор заготовки

В этом разделе пояснительной записки проанализируем два метода получения заготовок детали, а именно – заготовка из сортового проката и заготовка, получаемая литьем (по выплавляемым моделям)…

Разработка технологического процесса изготовления детали “Патрон”

2.5 Обоснование и выбор баз

Под базированием в машиностроении понимают придание заготовке или изделию требуемого положения относительно выбранной системы координат. Базирование необходимо на всех стадиях создания изделия: при конструкции и рассмотрении его в сборе…

Расчет привода главного движения радиально-сверлильного станка

1.8 Обоснование конструкции шпинделя, выбор материала, выбор термообработки

…

Система автоматического управления манипулятором робота-лунохода

4.1 Обоснование и выбор двигателя

В соответствии с ТЗ выбираемый двигатель должен обладать следующими характеристиками: 1. Ток якоря электродвигателя на валу при максимальной нагрузке не должен превышать 10А; 2. Двигатель должен запитываться от одной аккумуляторной батареи 12В…

Технология современных методов обработки деталей

3.2.1 Выбор и обоснование баз

Для достижения заданной точности обработки заготовок необходимо решить задачу базирования. Базированием достигается однозначное положение заготовки относительно зажимных элементов станка…

Турбина турбореактивного двухконтурного двигателя

1.

1.1 Выбор и обоснование параметров

1.1 Выбор и обоснование параметровВыбор параметров двигателя осуществляется в соответствии с рекомендациями, изложенными в пособии[1]. В зависимости от назначения и условий, при которых рассчитывается двигатель…

Условное обозначение м/с КР1533КП13:

| Назначение выводов КР1533КП13:

| Таблица режимов КР1533КП13

| Основные параметры КР1533КП13:

| ||

Мультиплексоры

ТЕОРЕТИЧЕСКАЯ ЧАСТЬ.

Мультиплексоры и демультиплексоры

отчет

по лабораторной работе №4

Выполнили: студент ИВТ-22 ________Иплаев А. Д. _________,

подпись дата

Проверил: к.т.н., доцент ________ Старыгин С.В. _________

подпись дата

Оценка _____________

Йошкар-Ола

2013 г.

Цель работы: знакомство с мультиплексорами и демультиплексорами.

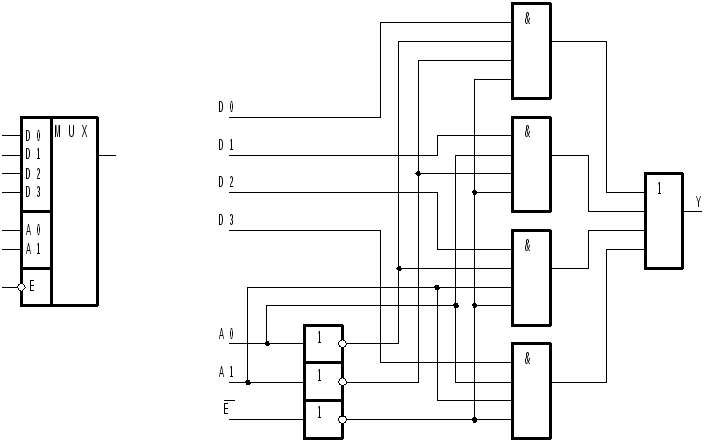

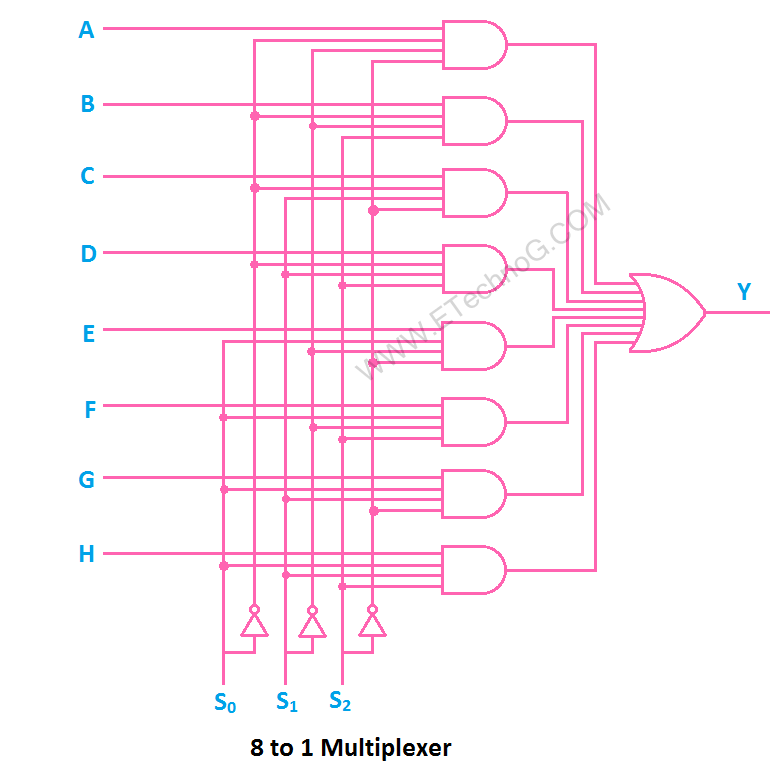

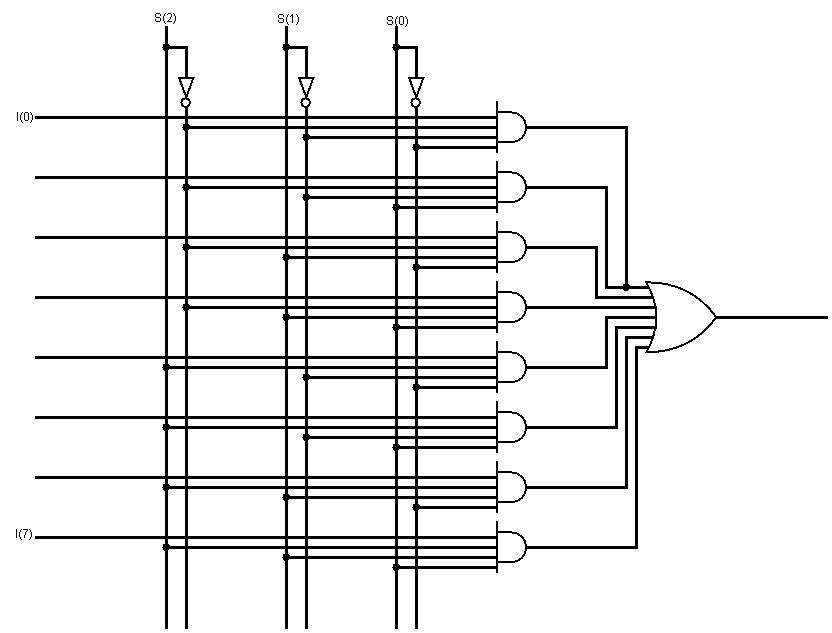

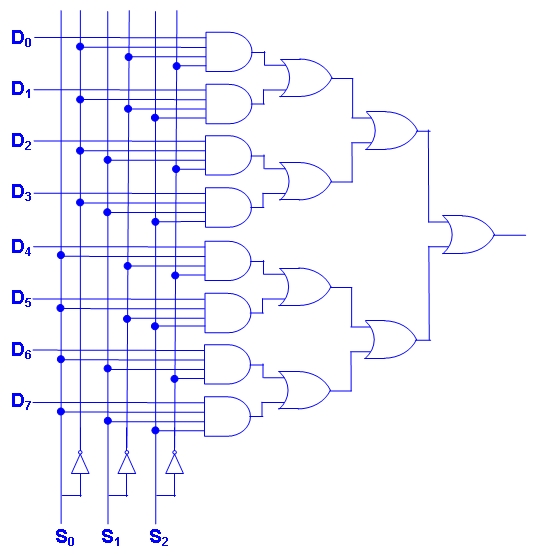

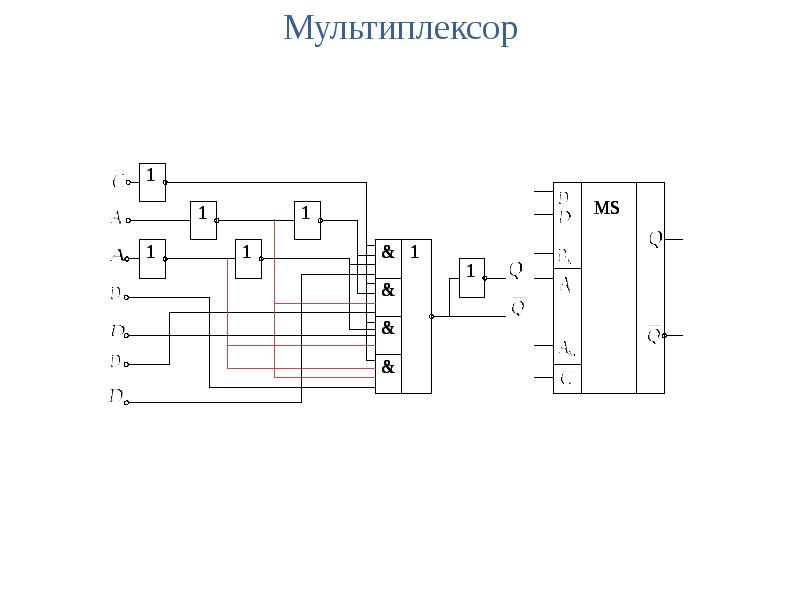

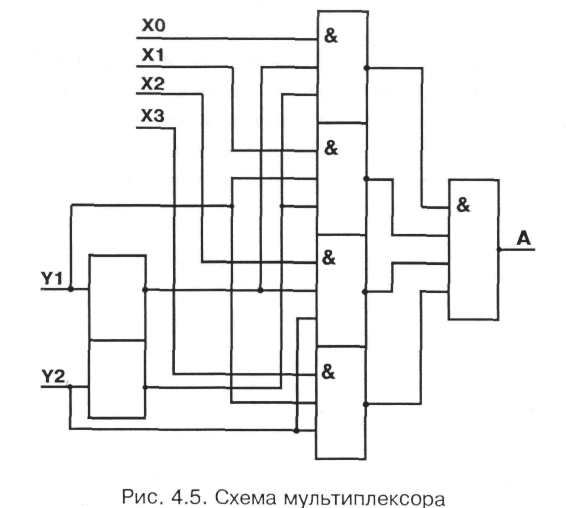

Мультиплексор (селектор) – комбинационная многовходовая схема с одним выходом. Входы мультиплексора подразделяются на информационные и управляющие. Для стандартных мультиплексоров справедливо соотношение n=2k, k – число управляющих входов, n – число информационных входов. Код, поступающий на управляющие входы, определяет один из информационных входов, сигнал с которого поступает на выход. Мультиплексор реализует функцию:

Код, поступающий на управляющие входы, определяет один из информационных входов, сигнал с которого поступает на выход. Мультиплексор реализует функцию:

F=Xi, если , где F – выход, Xi – i-ый информационный вход,

vi – i-ый управляющий вход, k – число управляющих входов.

Ниже приведена таблица состояний для мультиплексора с числом информационных входов n = 4; управляющих входов 2.

| v2 | v1 | x1 | x2 | x3 | x4 | F |

| x | x | x | ||||

| x | x | x | ||||

| x | x | x | ||||

| x | x | x | ||||

| x | x | x | ||||

| x | x | x | ||||

| x | x | x | ||||

| x | x | x |

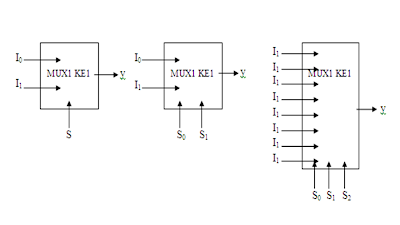

Стандартные схемы мультиплексоров имеют 4, 8 и 16 информационных входов. Для упрощенного описания мультиплексоры обозначают 4 в 1 (4®1), 8 в 1 (8®1) или

Для упрощенного описания мультиплексоры обозначают 4 в 1 (4®1), 8 в 1 (8®1) или

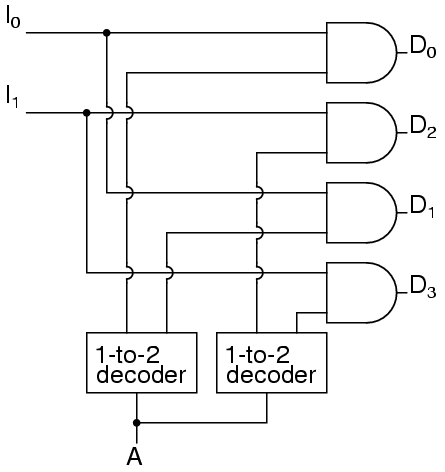

Рис. 53 Рис. 54

16 в 1 (16®1).

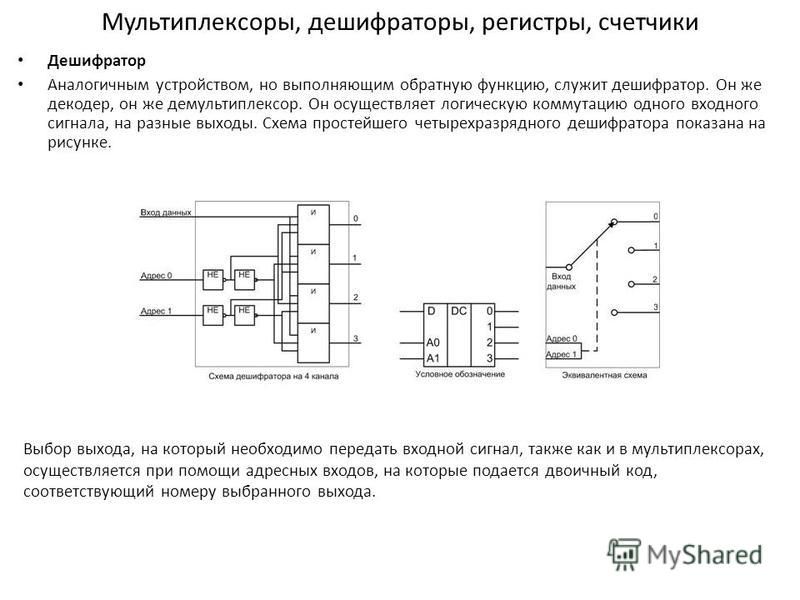

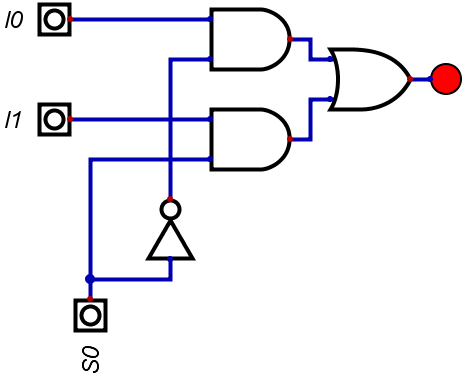

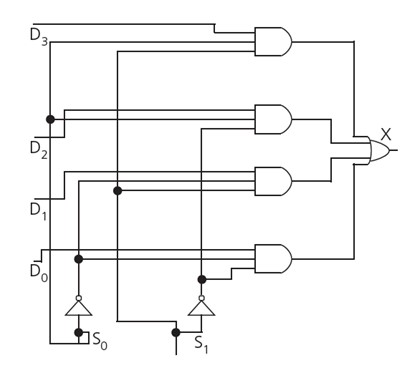

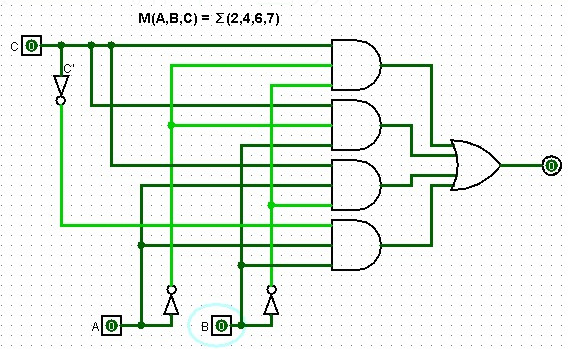

Функциональная схема мультиплексора 4 в 1 представленная на рис. 53, включает две ступени преобразования: дешифратор и составной логический элемент.

В двухступенчатой реализации мультиплексора общая задержка определяется задержками в дешифраторе и конъюнкторе. Для снижения задержки в реальных ИМС мультиплексоров используются линейные схемы (рис. 54)

Условное графическое обозначение мультиплексора представлено на рис. 55, а.

Рис. 55

Для расширения функциональных возможностей в мультиплексоры вводят управляющие сигналы E (Enable) или OE (Output enable). В первом случае реализуется мультиплексор со стробированием, во втором – с Z‑состоянием. На рис. 55, б представлена схема мультиплексора 2®1 со стробированием.

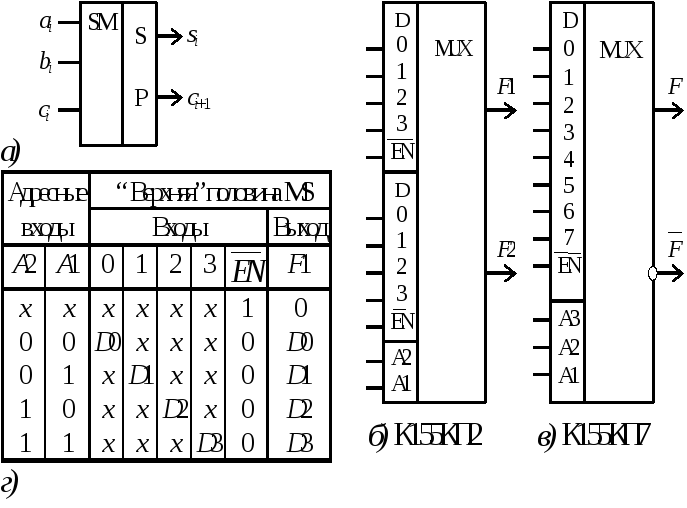

На рис. 56 и рис. 57 изображены УГО ИМС мультиплексоров.

КП5 – мультиплексор 8®1 (рис. 56, а).

56, а).

КП1 – MUX со стробированием 16®1 (рис. 56, б).

Рис. 56

КП2 – двухразрядный MUX 4®1 с общим управлением, со стробированием (рис. 55,в). КП19 – аналогичен КП2, но с инверсными выходами.

КП7 – мультиплексор 8®1 с прямыми и инверсными выходами .

КП16 – четырехразрядный мультиплексор 2®1 (рис.57, а). А – выбор четырехразрядного числа Х или Y. При А = 1 выбирается Y, при А = 0 – X. КП18 – аналогичен КП16, но с инверсными выходами DO.

КП11 – четырехразрядный мультиплексор 2®1 с Z-состоянием (рис. 57, б).

КП14 – четырехразрядный мультиплексор 2®1 с инверсными выходами ( ).

Рис. 57

КП12 – двухразрядный мультиплексор 4®1, аналог КП2, но с Z-состоянием.

КП17 – аналог КП12, но с инверсным выходом.

КП15 – мультиплексор 8®1 аналог КП7, но с Z-состоянием.

| Назначение, функциональные возможности | Тип | 133, Н133, КМ133 | 134, К134, КР134 | 155, К155, КМ155 | 199 | 530, М530, Н530, КМ530 | К531, КМ531, КР531 | 533, Н533 | 555, К555, КМ555 | К599 | КР1531 | 1533, КР1533 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Одновибратор | АГ1 | + | + | + | ||||||||

| Два одновибратора | АГ3 | + | +> | + | + | + | ||||||

| Два одновибратора | АГ4 | + | ||||||||||

| Сдвоенный формирователь | АП2 | + | + | |||||||||

| Двухканальный восьмиразрядный инвертирующий формирователь | АП3 | + | + | + | + | + | ||||||

| Двухканальный восьмиразрядный формирователь | АП4 | + | + | + | + | + | ||||||

| Восьмиканальный однонаправленный формирователь | АП5 | + | + | + | ||||||||

| Восьмиканальный двунаправленный формирователь | АП6 | + | + | + | ||||||||

| Восьмиканальный однонаправленный формирователь | АП14 | + | ||||||||||

| Восьмиканальный однонаправленный формирователь | АП16 | + | ||||||||||

| Двойной управляемый генератор | ГГ1 | + | + | |||||||||

| Приоритетный шифратор 8-3 | ИВ1 | + | + | + | + | |||||||

| Приоритетный шифратор 10-4 | ИВ3 | + | ||||||||||

| Двоично-десятичный дешифратор высоковольтный | ИД1 | + | + | |||||||||

| Дешифратор-демультиплексор 4*16 | ИД3 | + | + | + | + | + | ||||||

| Сдвоенный дешифрагор-мультиплексор 2×4 | ИД4 | + | + | + | + | + | ||||||

| Cдвоенный дешифратор-мультиплексор 2х4 с открытым коллектором | ИД5 | + | + | |||||||||

| Двоично-десятичный дешифратор 4*10 | ИД6 | + | + | + | ||||||||

| Двоичный дешифратор | ИД7 | + | + | + | + | + | ||||||

| Назначение, функциональные возможности | Тип | 133, Н133, КМ133 | 134, К134, КР134 | 155, К155, КМ155 | 199 | 530, М530, Н530, КМ530 | К531, КМ531, КР531 | 533, Н533 | 555, К555, КМ555 | К599 | КР1531 | 1533, КР1533 |

| Дешифратор для управления матрицей на светодиодах | ИД8 | + | ||||||||||

| ИД9 | + | |||||||||||

| Двоично-десятичный дешифратор | ИД10 | + | +> | + | + | |||||||

| Дешифратор 3*8: а) с запоминанием б) со сдвигом 1 точки в) со сдвигом 2 точек | ИД11 | + | ||||||||||

| ИД12 | + | |||||||||||

| ИД13 | + | |||||||||||

| Два дешифратора-демультиплексора 2*4 | ИД14 | + | + | |||||||||

| Дешифратор для управления шкалой красного цвета | ИД15 | + | + | |||||||||

| Дешифратор для управления шкалой зеленого или желтого цвета | ИД16 | + | ||||||||||

| Дешифратор состояний | ИД17 | + | ||||||||||

| Дешифратор двоично-десятичного кода в информацию для семисегментного индикатора | ИД18 | + | ||||||||||

| Дешифратор-демультиплексор 4х16 | ИД19 | + | ||||||||||

| Декадный счетчик | ИЕ1 | + | ||||||||||

| Четырехразрядный двоично-десятичный счетчик | ИЕ2 | + | + | + | + | |||||||

| Счетчик-делитель | ИЕ4 | + | + | |||||||||

| Двоичный счетчик | ИЕ5 | + | + | + | + | + | ||||||

| Двоично-десятичный реверсивный счетчик | ИЕ6 | + | + | + | + | + | ||||||

| Назначение, функциональные возможности | Тип | 133, Н133, КМ133 | 134, К134, КР134 | 155, К155, КМ155 | 199 | 530, М530, Н530, КМ530 | К531, КМ531, КР531 | 533, Н533 | 555, К555, КМ555 | К599 | КР1531 | 1533, КР1533 |

| Четырехразрядный двоичный реверсивный счетчик | ИЕ7 | + | + | + | + | + | ||||||

| Делитель частоты с переменным коэффициентом деления | ИЕ8 | + | + | |||||||||

| Четырехразрядный десятичный синхронный счетчик | ИЕ9 | + | + | + | + | |||||||

| Четырехразрядный двоичный синхронный счетчик | ИЕ10 | + | + | + | + | |||||||

| Четырехразрядный двоичный синхронный счетчик | ИЕ11 | + | ||||||||||

| Четырехразрядный двоичный синхронный счетчик | ИЕ13 | + | ||||||||||

| Двоично-десятичный счетчик | ИЕ14 | + | + | + | + | + | ||||||

| Двоичный счетчик асинхронный | ИЕ15 | + | + | + | + | |||||||

| Четырехразрядный десятичный реверсивный счетчик | ИЕ16 | + | + | |||||||||

| Четырехразрядный двоичный реверсивный счетчик | ИЕ17 | + | + | |||||||||

| Четырехразрядный двоичный синхронный счетчик | ИЕ18 | + | + | |||||||||

| Два четырехразрядных счетчика | ИЕ19 | + | ||||||||||

| Назначение, функциональные возможности | Тип | 133, Н133, КМ133 | 134, К134, КР134 | 155, К155, КМ155 | 199 | 530, М530, Н530, КМ530 | К531, КМ531, КР531 | 533, Н533 | 555, К555, КМ555 | К599 | КР1531 | 1533, КР1533 |

| Схема быстрого умножителя 2*4 разряда | ИК1 | + | + | |||||||||

| Арифметическо-логическое устройство с умножением | ИК2 | + | ||||||||||

| Одноразрядный полный сумматор | ИМ1 | + | + | |||||||||

| Двухразрядный полный сумматор | ИМ2 | + | + | |||||||||

| Четырехразрядный двоичный сумматор | ИМ3 | + | + | |||||||||

| Четырехразрядный полный сумматор | ИМ4 | + | ||||||||||

| Два одноразрядных двоичных полных сумматора | ИМ5 | + | + | + | ||||||||

| Четырехразрядный двоичный сумматор с ускоренным переносом | ИМ6 | + | + | |||||||||

| Четырехразрядный сумматор-вычитатель | ИМ7 | + | + | |||||||||

| 8-разрядная схема контроля четности и нечетности | ИП2 | + | + | + | ||||||||

| АЛУ для записи двух 4-разрядных слов | ИП3 | + | + | + | + | + | + | + | + | |||

| Схема ускоренного переноса для АЛУ | ИП4 | + | + | + | + | + | + | + | + | |||

| 9-разрядная схема контроля четности | ИП5 | + | + | + | + | + | ||||||

| 4-шинный приемопередатчик с инверсными выходами | ИП6 | + | + | + | ||||||||

| 4-шинный приемопередатчик | ИП7 | + | + | + | ||||||||

| 8-разрядный последовательно-параллельный двоичный перемножитель | ИП9 | + | ||||||||||

| Назначение, функциональные возможности | Тип | 133, Н133, КМ133 | 134, К134, КР134 | 155, К155, КМ155 | 199 | 530, М530, Н530, КМ530 | К531, КМ531, КР531 | 533, Н533 | 555, К555, КМ555 | К599 | КР1531 | 1533, КР1533 |

| 4-разрядный универсальный сдвиговый регистр | ИР1 | + | + | + | ||||||||

| 8-разрядный сдвигающий регистр | ИР2 | + | ||||||||||

| 4-разрядный селективный накопительный регистр | ИР5 | + | ||||||||||

| 8-разрядный последовательный сдвигающий регистр с параллельным выходом | ИР8 | + | + | + | ||||||||

| 8-разрядный сдвиговый регистр с параллельным вводом информации | ИР9 | + | + | |||||||||

| 8-разрядный сдвиговый регистр | ИР10 | + | ||||||||||

| 4-разрядный универсальный регистр сдвига | ИР11 | + | + | + | + | |||||||

| 4-разрядный сдвиговый регистр с параллельным вводом информации | ИР12 | + | + | |||||||||

| 8-разрядный реверсивный сдвиговый регистр | ИР13 | + | + | |||||||||

| 4-разрядный регистр | ИР15 | + | + | |||||||||

| 4-разрядный универсальный регистр сдвига | ИР16 | + | + | |||||||||

| 12-разрядный регистр последовательного приближения | ИР17 | + | + | |||||||||

| 6-разрядный параллельный регистр с D-триггерами | ИР18 | + | + | |||||||||

| 4-разрядный параллельный регистр с D-триггерами | ИР19 | + | + | |||||||||

| 4-разрядный двухвходовый регистр | ИР20 | + | + | |||||||||

| 4-разрядное сдвигающее устройство | ИР21 | + | + | |||||||||

| Назначение, функциональные возможности | Тип | 133, Н133, КМ133 | 134, К134, КР134 | 155, К155, КМ155 | 199 | 530, М530, Н530, КМ530 | К531, КМ531, КР531 | 533, Н533 | 555, К555, КМ555 | К599 | КР1531 | 1533, КР1533 |

| 8-разрядный регистр на D-триггерах с потенциальным входом | ИР22 | + | + | + | + | + | ||||||

| 8-разрядный регистр на D-триггерах с динамическим входом | ИР23 | + | + | + | + | + | ||||||

| 8-разрядный универсальный сдвиговый регистр | ИР24 | + | + | |||||||||

| 4-разрядный регистр с импульсным управлением | ИР25 | + | ||||||||||

| Регистровый файл 4 слова на 4 разряда | ИР26 | + | + | |||||||||

| 8-разрядный регистр | ИР27 | + | + | |||||||||

| 8-разрядный последовательно-параллельный регистр | ИР28 | + | ||||||||||

| 8-разрядный регистр хранения с адресацией | ИР30 | + | ||||||||||

| 24-разрядный последовательный регистр сдвига | ИР31 | + | ||||||||||

| Регистровый файл 4 слова на 4 разряда с открытым коллекторным выходом | ИР32 | + | + | |||||||||

| 8-разрядный буферный регистр | ИР33 | + | ||||||||||

| Два 4-разрядных буферных регистра | ИР34 | + | ||||||||||

| 8-разрядный буферный регистр с импульсным управлением | ИР37 | + | ||||||||||

| Два 4-разрядных регистра D-типа | ИР38 | + | ||||||||||

| БИС регистров общего назначения с многоканальным доступом | ИР39 | + | ||||||||||

| Назначение, функциональные возможности | Тип | 133, Н133, КМ133 | 134, К134, КР134 | 155, К155, КМ155 | 199 | 530, М530, Н530, КМ530 | К531, КМ531, КР531 | 533, Н533 | 555, К555, КМ555 | К599 | КР1531 | 1533, КР1533 |

| Селектор-мультиплексор на 16 каналов со стробированием | КП1 | + | + | |||||||||

| Сдвоенный цифровой селектор-мультиплексор 4-1 | КП2 | + | + | + | + | + | + | + | ||||

| Селектор-мультиплексор на 8 каналов | КП5 | + | + | |||||||||

| Селектор-мультиплексор на 8 каналов со стробированием | КП7 | + | + | + | + | + | + | + | ||||

| Три схемы переключателя | КП8 | + | ||||||||||

| Сдвоенный коммутатор 4 каналов в 1 | КП9 | + | ||||||||||

| Коммутатор 8 каналов в 1 | КП10 | + | ||||||||||

| 4-разрядный селектор-мультиплексор 2 в 1 с тремя состояниями | КП11 | + | + | + | + | + | ||||||

| 2-разрядный 4-канальный коммутатор | КП12 | + | + | + | + | |||||||

| Четыре 2-входовых мультиплексора с запоминанием | КП13 | + | + | + | ||||||||

| 4-разрядный селектор-мультиплексор 2 каналов в 1 с инверсией и тремя состояниями | КП14 | + | + | + | + | + | ||||||

| 8-входовый селектор-мультиплексор | КП15 | + | + | + | + | + | ||||||

| 4-разрядный селектор-мультиплексор 2 каналов в 1 | КП16 | + | + | + | + | |||||||

| Сдвоенный инверсный селектор- мультиплексор 4 каналов в 1 с тремя состояниями | КП17 | + | ||||||||||

| 4-разрядный селектор- мультиплексор 2 каналов в 1 с инверсными выходами | КП18 | + | + | |||||||||

| Сдвоенный селектор-мультиплексор 4 каналов в 1 | КП19 | + | ||||||||||

| Назначение, функциональные возможности | Тип | 133, Н133, КМ133 | 134, К134, КР134 | 155, К155, КМ155 | 199 | 530, М530, Н530, КМ530 | К531, КМ531, КР531 | 533, Н533 | 555, К555, КМ555 | К599 | КР1531 | 1533, КР1533 |

| Два логических элемента 4И-НЕ | ЛА1 | + | + | + | + | + | + | + | + | |||

| Логический элемент 8И-НЕ | ЛА2 | + | + | + | + | + | + | + | + | |||

| Четыре логических элемента 2И-НЕ | ЛАЗ | + | + | + | + | + | + | + | + | |||

| Три логических элемента 3И-НЕ | ЛА4 | + | + | + | + | + | + | + | + | |||

| Два логических элемента 4И-НЕ с повышенной нагрузочной способностью | ЛА6 | + | + | + | + | |||||||

| Два логических элемента 4И-НЕ с открытым коллекторным выходом | ЛА7 | + | + | + | + | + | + | |||||

| Четыре логических элемента 2И-НЕ с открытым коллекторным выходом | ЛА8 | + | + | + | + | |||||||

| Четыре логических элемента 2И-НЕ с открытым коллекторным выходом | ЛА9 | + | + | + | + | + | ||||||

| Три логических элемента 3И-НЕ с открытым коллекторным выходом | ЛА10 | + | + | + | + | |||||||

| Четыре логических элемента 2И-НЕ с открытым коллекторным выходом, высоковольтных | ЛА11 | + | + | |||||||||

| Четыре логических элемента 2И-НЕ с высокой нагрузочной способностью | ЛА12 | + | + | + | + | + | + | |||||

| Четыре логических элемента 2И-НЕ с открытым коллектором и высокой нагрузочной способностью | ЛА13 | + | + | + | + | |||||||

| Четыре логических элемента 2И-НЕ сопряжения микросхем МОП ЗУ-ТТЛ | ЛА15 | + | ||||||||||

| Два логических элемента 4И-НЕ (магистральный усилитель) | ЛА16 | + | + | |||||||||

| Два логических элемента 4И-НЕ с тремя состояниями на выходе | ЛА17 | + | + | |||||||||

| Два логических элемента 2И-НЕ с мощным открытым коллекторным выходом | ЛА18 | + | ||||||||||

| Логический элемент 12И-НЕ с тремя состояниями на выходе | ЛА19 | + | ||||||||||

| Назначение, функциональные возможности | Тип | 133, Н133, КМ133 | 134, К134, КР134 | 155, К155, КМ155 | 199 | 530, М530, Н530, КМ530 | К531, КМ531, КР531 | 533, Н533 | 555, К555, КМ555 | К599 | КР1531 | 1533, КР1533 |

| Четыре логических элемента 2И-НЕ/2ИЛИ-НЕ | ЛБ1 | + | ||||||||||

| Два логических элемента 4 И-НЕ/4 ИЛИ-НЕ и логический элемент НЕ | ЛБ2 | + | ||||||||||

| Два 4-входовых логических расширителя по ИЛИ | ЛД1 | + | + | + | ||||||||

| 8-входовый расширитель по ИЛИ | ЛД3 | + | + | |||||||||

| Четыре логических элемента 2 ИЛИ-НЕ | ЛЕ1 | + | + | + | + | + | + | + | + | |||

| Два 4-входовых логических элемента ИЛИ-НЕ со стробированием на одном и расширением по ИЛИ на другом | ЛЕ2 | + | ||||||||||

| Два логических элемента 4 ИЛИ-НЕ со стробированием | ЛЕ3 | + | + | |||||||||

| Три логических элемента 3 ИЛИ-НЕ | ЛЕ4 | + | + | + | ||||||||

| Четыре логических элемента 2 ИЛИ-НЕ буферных | ЛЕ5 | + | + | |||||||||

| Четыре логических элемента 2 ИЛИ-НЕ, магистральный усилитель | ЛЕ6 | + | + | |||||||||

| Два логических элемента 5 ИЛИ-НЕ | ЛЕ7 | + | ||||||||||

| Четыре логических элемента 2И | ЛИ1 | + | + | + | + | + | + | + | + | + | ||

| Четыре логических элемента 2И с открытым коллекторным выходом | ЛИ2 | + | + | |||||||||

| Три логических элемента 3И | ЛИ3 | + | + | + | + | + | ||||||

| Три логических элемента 3И с открытым коллекторным выходом | ЛИ4 | + | ||||||||||

| Два логических элемента 2И с мощным открытым коллекторным выходом | ЛИ5 | + | + | |||||||||

| Два логических элемента 4И | ЛИ6 | + | + | |||||||||

| Назначение, функциональные возможности | Тип | 133, Н133, КМ133 | 134, К134, КР134 | 155, К155, КМ155 | 199 | 530, М530, Н530, КМ530 | К531, КМ531, КР531 | 533, Н533 | 555, К555, КМ555 | К599 | КР1531 | 1533, КР1533 |

| Логический элемент 4И- 2ИЛИ- НЕ/4 И-2 ИЛИ с возможностью расши рения по ИЛИ | ЛК1 | + | + | |||||||||

| Два логических элемента 2 (2- 2И- 2ИЛИ- НЕ / 2- 2И- 2ИЛИ) | ЛК3 | + | + | |||||||||

| Логический элемент 2- 2- 2- 2И- 4ИЛИ- НЕ / 2- 2- 2- 2И- 4ИЛИ с возможностью расширения по ИЛИ | ЛК4 | |||||||||||

| Логический элемент 8H-НЕ/8И с возможностью расширения по ИЛИ | ЛК5 | + | + | |||||||||

| Два логических элемента 2И- 2И- 2ИЛИ / 2И- 2И- 2ИЛИ- НЕ | ЛК6 | + | + | |||||||||

| Логический элемент 2И- 2И- 2И- 2И- 4ИЛИ / 2И- 2И- 2И- 2И- 4ИЛИ- НЕ с возможностью расширения по ИЛИ | ЛК7 | + | ||||||||||

| Четыре логических элемента 2ИЛИ | ЛЛ1 | + | + | + | + | + | + | + | ||||

| Два логических элемента 2ИЛИ с мощным открытым коллекторным выходом | ЛЛ2 | + | ||||||||||

| Шесть логических элементов НЕ | ЛН1 | + | + | + | + | + | + | + | + | |||

| Шесть логических элементов НЕ с открытым коллекторным выходом | ЛН2 | + | + | + | + | + | + | + | ||||

| Шесть буферных логических элементов НЕ с повышенным коллекторным напряжением | ЛНЗ | + | + | |||||||||

| 6 элементов НЕ с открытым коллектором | ЛН4 | |||||||||||

| Шесть буферных логических элементов НЕ | ЛН5 | + | + | |||||||||

| Шесть логических элементов НЕ с тремя состояниями на выходе | ЛН6 | + | ||||||||||

| Назначение, функциональные возможности | Тип | 133, Н133, КМ133 | 134, К134, КР134 | 155, К155, КМ155 | 199 | 530, М530, Н530, КМ530 | К531, КМ531, КР531 | 533, Н533 | 555, К555, КМ555 | К599 | КР1531 | 1533, КР1533 |

| Два приемника сигналов с парафазным входом и выходом | ЛП1 | + | ||||||||||

| Три логических элемента мажоритарной логики 2-2-2-И-3 ИЛИ-НЕ | ЛП3 | + | + | + | ||||||||

| Шесть буферных формирователей с открытым коллектором | ЛП4 | + | ||||||||||

| Четыре 2-входовых элемента «исключающее ИЛИ» | ЛП5 | + | + | + | + | + | + | + | ||||

| Два логических элемента 2И-НЕ с общим входом и двумя мощными транзисторами | ЛП7 | + | + | |||||||||

| Четыре буферных элемента с тремя состояниями на выходе | ЛП8 | + | + | + | + | |||||||

| Шесть буферных формирователей с открытым коллектором и повышен ным коллекторным напряжением | ЛП9 | + | + | |||||||||

| Шесть повторителей с элементом управления по входам и тремя со стояниями на выходе | ЛП10 | + | ||||||||||

| Шесть повторителей с раздельными элементами управления входами по двум и четырем повторителям с тремя состояниями на выходе | ЛП11 | + | ||||||||||

| Четыре 2-входовых логических элемента «исключающее ИЛИ» с от крытым коллекторным выходом | ЛП12 | + | ||||||||||

| Назначение, функциональные возможности | Тип | 133, Н133, КМ133 | 134, К134, КР134 | 155, К155, КМ155 | 199 | 530, М530, Н530, КМ530 | К531, КМ531, КР531 | 533, Н533 | 555, К555, КМ555 | К599 | КР1531 | 1533, КР1533 |

| Два логических элемента 2-2И-2ИЛИ-НЕ, один расширяемый по ИЛИ | ЛР1 | + | + | + | ||||||||

| Логический элемент 2И-2И-3И-4ИЛИ-НЕ | ЛР2 | + | ||||||||||

| Логический элемент 2-2-2-3И-4ИЛИ-НЕ с возможностью расширения по ИЛИ | ЛР3 | + | + | |||||||||

| Логический элемент 4И-2ИЛИ-НЕ с возможностью расширения по ИЛИ | ЛР4 | + | + | + | + | + | + | |||||

| Логический элемент 4-2-2-3И-4ИЛИ-НЕ | ЛР9 | + | + | |||||||||

| Логический элемент 4-2-2-3И-4ИЛИ-НЕ с открытым коллекторным выходом | ЛР10 | + | ||||||||||

| Два логических элемента 2-2(3-3)И-2ИЛИ-НЕ | ЛР11 | + | + | + | + | + | ||||||

| Логический элемент (2-3-3-2)И-4ИЛИ-НЕ | ЛР13 | + | + | + | ||||||||

| Преобразователь двоично-десятичного кода в двоичный | ПР6 | + | ||||||||||

| Преобразователь двоичного кода в двоично-десятичный | ПР7 | + | ||||||||||

| Схема сравнения двух 4-разрядных чисел | СП1 | + | + | + | + | + | + | |||||

| JК – триггер с логикой ЗИ на входе | ТВ1 | + | + | + | ||||||||

| Два JK-триггера со сбросом | ТВ6 | + | + | |||||||||

| Два JK-триггера с установкой «О» и «1» | ТВ9 | + | + | + | + | |||||||

| Два JK-триггера с установкой «1» | ТВ10 | + | + | |||||||||

| Два JK-триггера с раздельной установкой «1» и общими установкой нуля и синхронизацией | ТВ11 | + | + | |||||||||

| Два JK-триггера | ТВ14 | + | ||||||||||

| Два JK-триггера | ТВ15 | + | + | + | ||||||||

| Два триггера Шмитта с логическим элементом на входе 4И-НЕ | ТЛ1 | + | + | |||||||||

| Шесть триггеров Шмитта | ТЛ2 | + | + | + | + | |||||||

| Четыре 2-входовых триггера Шмитта | ТЛ3 | + | + | + | + | |||||||

| Два D-триггера | ТМ2 | + | + | + | + | + | + | + | + | |||

| Четыре D-триггера | ТМ5 | + | + | |||||||||

| Четыре D-триггера с прямыми и инверсными выходами | ТМ7 | + | + | + | + | |||||||

| Четыре синхронных D-триггера | ТМ8 | + | + | + | + | + | + | |||||

| Шесть синхронных D-триггеров | ТМ9 | + | + | + | + | + | ||||||

| Четыре RS-триггера | ТР2 | + | + | + | ||||||||

| Многофункциональный элемент для ЭВМ | ХЛ1 | + | + |

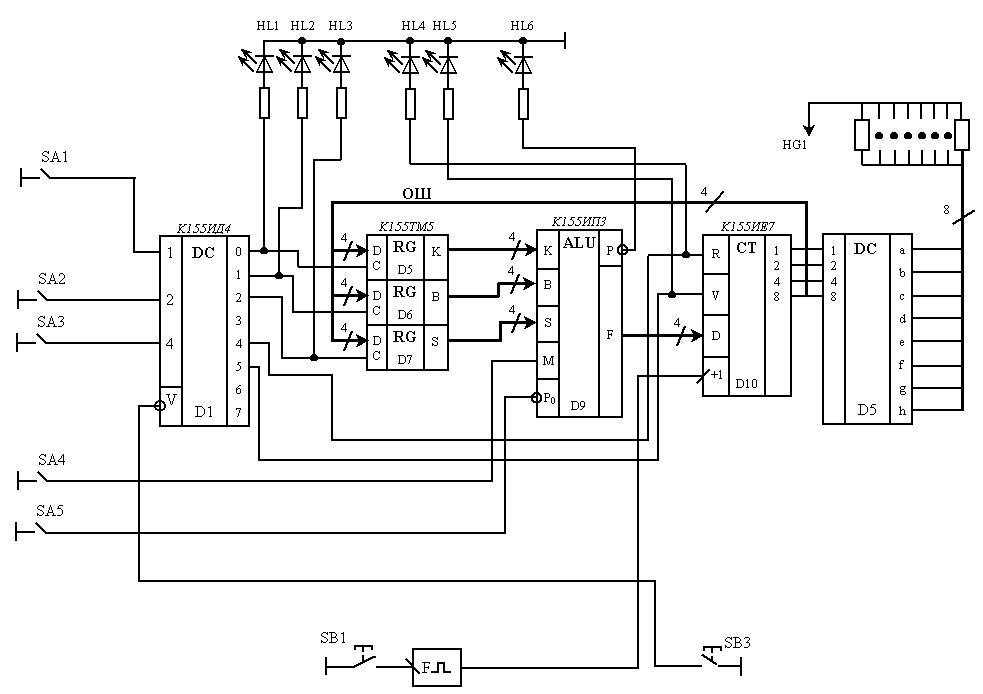

Проектирование процессора Logisim / Хабр

Часть IЧасть II

Часть III

Часть IV

Часть V

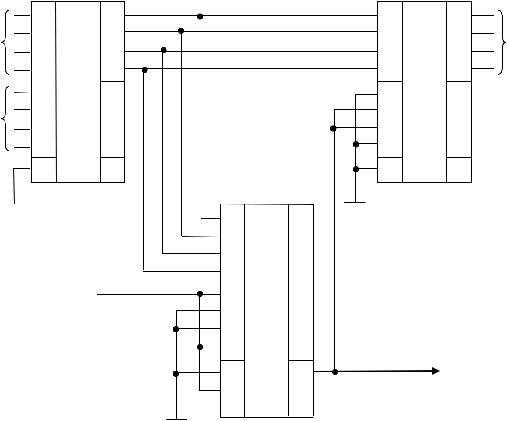

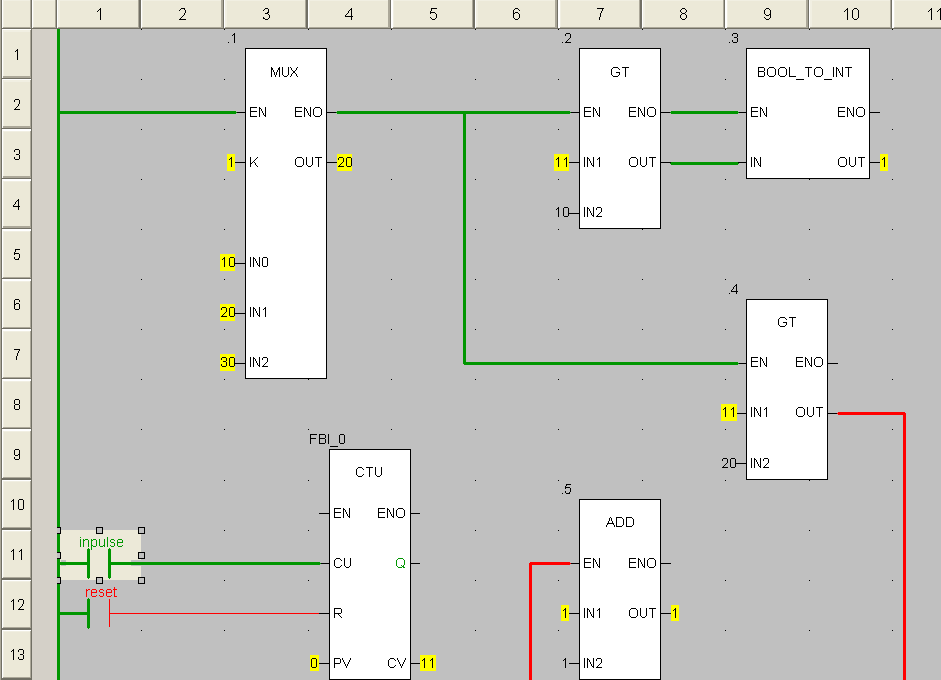

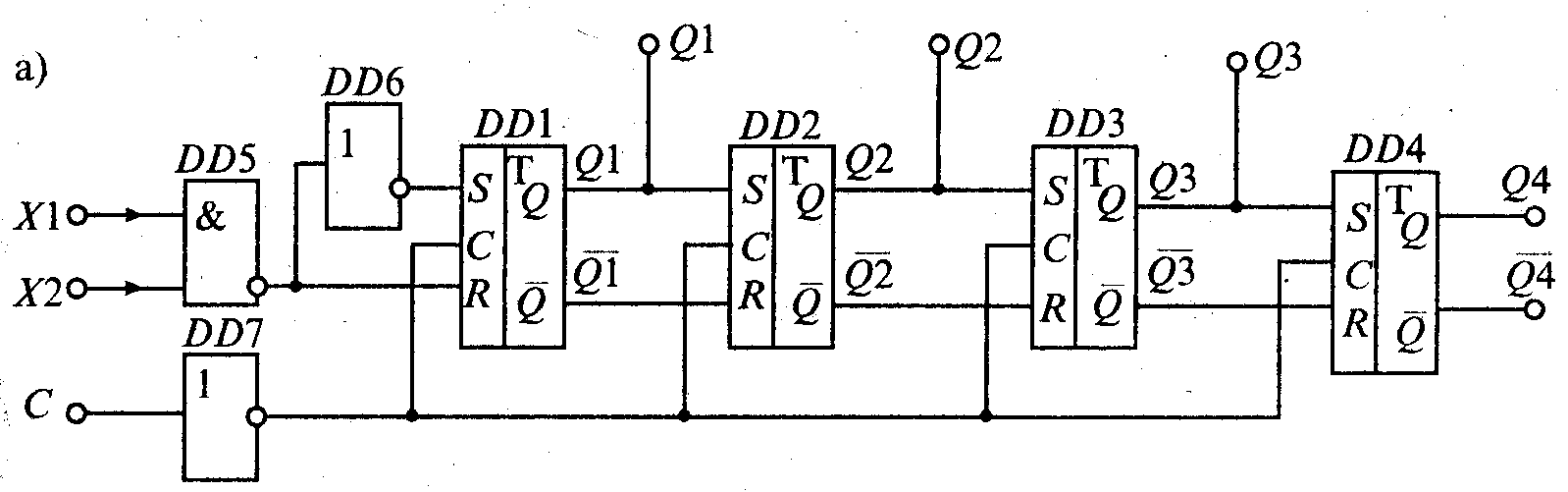

Одна из глав книги «Код» Чарльза Петцольда посвящена проектированию CPU и в начале главы описывается устройство, позволяющие суммировать наборы чисел, хранящихся в памяти. Спроектируем эту схему в Logisim. Возьмем набор восьмиразрядных чисел и подключим его к мультиплексору, переход от одного числа к другому будем осуществлять с помощью счетчика, подключенного к выбирающему входу мультиплексора, а к выходу мультиплексора подключим сумматор и аккумулятор. В качестве тактового генератора будем использовать кнопку. Данные будут загружаться в аккумулятор при отпускании кнопки (это осуществляется с помощью элемента НЕ, подключенного к кнопке).

Спроектируем эту схему в Logisim. Возьмем набор восьмиразрядных чисел и подключим его к мультиплексору, переход от одного числа к другому будем осуществлять с помощью счетчика, подключенного к выбирающему входу мультиплексора, а к выходу мультиплексора подключим сумматор и аккумулятор. В качестве тактового генератора будем использовать кнопку. Данные будут загружаться в аккумулятор при отпускании кнопки (это осуществляется с помощью элемента НЕ, подключенного к кнопке).

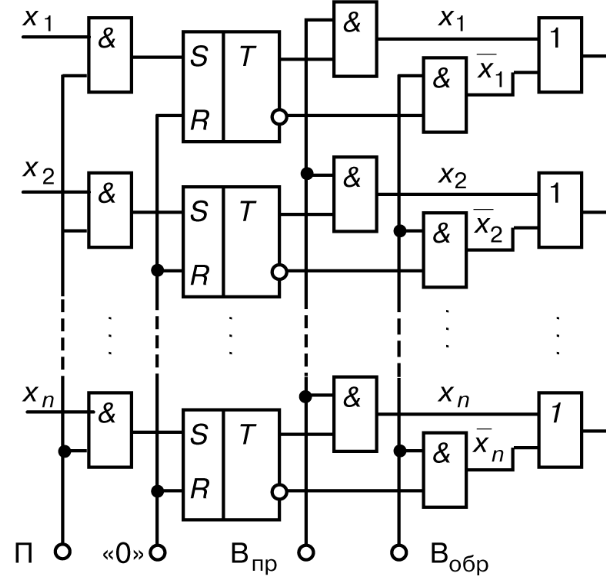

Будем хранить числа в ОЗУ (RAM).

ОЗУ можно представить в виде набора регистров, доступ к которым производится с помощью демультиплексора и мультиплексора (DMX и MUX).

Гарвардская архитектура

Предположим, в ОЗУ хранится набор чисел, а нам нужно сложить все числа и сохранить результат (в свободную ячейку). Будем хранить команды («сложить» и «сохранить») в одном ОЗУ, а обрабатываемые числа — в другом. Такой способ хранения является отличительным признаком

Гарвардской архитектуры.

Команда «1» будет записывать число из сумматора в аккумулятор, команда «2» будет записывать число из аккумулятора во 2-ое ОЗУ.

Предположим, в ОЗУ хранятся несколько массивов чисел. Т.е. нам необходимо

- загружать числа из ОЗУ в аккумулятор

- загружать числа из сумматора в аккумулятор

- сохранять числа из аккумулятора в ОЗУ

Будем использовать для выборки данных из ОЗУ мультиплексор MUX.

Новая инструкция «5» по переднему фронту тактового генератора переключает мультиплексор MUX, а по заднему фронту (по спаду) производит запись в аккумулятор.

Архитектура фон Неймана

Далее, будем хранить инструкции и данные в одном ОЗУ. Такой способ хранения является отличительным признаком

архитектуры фон Неймана.

В первых четырех разрядах восьмиразрядной ячейки памяти будет храниться команда, во вторых четырех разрядах будет храниться адрес (

прямая адресация).

Будем загружать адрес и команду в отдельные регистры, а затем с помощью мультиплексора переходить по сохраненному адресу. Для записи данных в ОЗУ будем сначала загружать данные во временный регистр Temp (иначе в ОЗУ запишутся инструкции, а не данные), а потом в аккумулятор Асс. Запись данных в Temp и Асс будем производить по заднему фронту.

Для записи данных в ОЗУ будем сначала загружать данные во временный регистр Temp (иначе в ОЗУ запишутся инструкции, а не данные), а потом в аккумулятор Асс. Запись данных в Temp и Асс будем производить по заднему фронту.

Будем складывать, например, числа 2 и 3, которые лежат в ячейках 8 и 9, а сохранять результат в ячейку с адресом a.

Добавим также возможность совершать безусловные переходы.

Реализуем устройство, в котором будет выполняться всего одна команда — команда безусловного перехода. Для этого на счетчик, генерирующий адрес, будем отправлять четыре младших разряда (собственно, адрес), а на порт загрузки будем подавать команду, хранящуюся в старших разрядах ячейки памяти.

Например, для прыжка в ячейку с адресом 2 используется команда 82.

Добавим команду безусловного перехода в предыдущую схему.

Вообще, на geektimes уже была статья, посвященная проектированию CPU в Logisim.

Все схемы, представленные выше, можно скачать одним файлом.

Logisim можно скачать здесь.

Терминал

Добавим к схеме терминал для демонстрации того, как ассемблерные инструкции преобразуются в машинный код.

Добавим

конечный автоматдля обработки последовательностей поступающих символов.

Семизначный код буквы «i» равняется

1101001Семизначный код буквы «n» равняется

1101110Семизначный код буквы «p» равняется

1110000Для выделения конкретной буквы из потока символов будем использовать компаратор. В начальном состоянии компаратор сравнивает поступивший символ с семизначным кодом буквы «i»

Автомат переходит в следующее состояние, если после буквы «i» поступает буква «n»

Автомат переходит в следующее состояние, если после букы «i», а затем «n» поступает буква «p»

Добавим команду out

Подробнее о командах inp и out можно прочитать в следующей части.

Железо

Рассмотрим, как работает сумматор на примере микросхемы 155им3 (7483). Для микросхем 155-й серии условимся, что на входах есть внутренний резистор, подтягивающий к плюсу (если ножка «висит в воздухе», то на ней присутствует логическая «единица»), поэтому при подключении питания к микросхеме зажгутся все светодиоды, присоединенные к выходу.

Для микросхем 155-й серии условимся, что на входах есть внутренний резистор, подтягивающий к плюсу (если ножка «висит в воздухе», то на ней присутствует логическая «единица»), поэтому при подключении питания к микросхеме зажгутся все светодиоды, присоединенные к выходу.

На картинке представлена МС 74ls283 (современный аналог 155им3).

Для того, чтобы в Logisim спроектировать такую микросхему, необходимо выбрать «Меню» — «Проект» — «Добавить схему».

Вот как эта МС выглядит внутри подсхемы. Это четыре полусумматора, объединённые в полный сумматор.

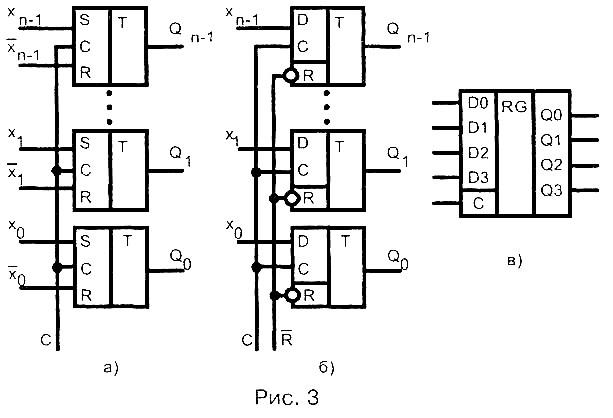

В качестве аккумулятора будем использовать микросхему 155тм8 (74175) — счетверённый D-триггер.

Триггеры, входящие в состав МС, пропускают насквозь всё время, пока на входе синхронизации присутствует 1, а не только по фронту (триггеры со статическим управлением), но в программе Logisim нам доступны только триггеры с динамическим управлением, но в данном случае это не важно; будем использовать то, что есть.

Подробнее про триггеры можно прочитать в Википедии.

Соберём из D-триггеров модель МС 155тм8.

Далее соберём схему, позволяющую складывать наборы чисел.

Например, если сложить набор из чисел 2 (0010), мы получим 2 (0010), 4 (0100), 6 (0110) и т.д.

Сперва 2 появляется на выходе сумматора (красные светодиоды), затем 2 загружается в счетверенный D-тригер (желтые светодиоды), а на выходе сумматора появляется 4, затем 4 загружается в 155тм8, а на выходе сумматора появляется 6 и т.д.

Для того, чтобы спроектировать простой модуль памяти, нам понадобится мультиплексор. Спроектируем сдвоенный мультиплексор 155кп2.

Также нам понадобится счетчик. Спроектируем микросхему 155ие5.

Это четырехразрядный счетчик, но нам понадобится только два младших разряда.

Будем хранить числа, например, 2 (0010), 3 (0011), 5 (0101).

Объединим все компоненты в одну схему. Будем складывать числа, которые хранятся в «памяти»

2 + 3 + 5.

Logisim можно скачать здесь.

P.S. Статья про книгу «Код. Тайный язык информатики.» есть на Хабре вот здесь.

Статья про книгу «Код. Тайный язык информатики.» есть на Хабре вот здесь.

З.Ы. Переводные статьи (автор переводов PatientZero) про архитектуру процессора здесь, здесь и здесь

Демонстрация мультиплексора и демультиплексора (4 бита) На изображении выше показан эскиз

интерактивный Java-апплет, встроенный в эту страницу.

К сожалению, ваш браузер не поддерживает Java.

или Java отключена в настройках браузера. Чтобы запустить апплет, включите Java

и перезагрузите эту страницу.

(Возможно, вам придется перезапустить браузер.) Описание цепи Этот апплет демонстрирует функцию 2-битного и 4-битного мультиплексор и демультиплексор компонентов.

Будет показана внутренняя структура этих компонентов.

в следующем апплете (ах).

Пожалуйста, поиграйте с выбранными переключателями входа, чтобы изучить поведение

компонентов. Схема мультиплексора работает аналогично стандартному многоходовому переключателю.

Он передает выбранный вход напрямую на единственный выход.Типичное использование – выбор нового входного значения для триггера из

набор из нескольких альтернатив. В демонстрационных целях вводы данных мультиплексоров

не все связаны со статическими входными значениями,

но также и к двум генераторам часов с разными периодами синхронизации.

Это должно позволить вам напрямую «видеть», какой входной сигнал

передается мультиплексором. Демультиплексор выполняет функцию, обратную мультиплексору. Чтобы запустить апплет, включите Java

и перезагрузите эту страницу.

(Возможно, вам придется перезапустить браузер.) Описание цепи Этот апплет демонстрирует функцию 2-битного и 4-битного мультиплексор и демультиплексор компонентов.

Будет показана внутренняя структура этих компонентов.

в следующем апплете (ах).

Пожалуйста, поиграйте с выбранными переключателями входа, чтобы изучить поведение

компонентов. Схема мультиплексора работает аналогично стандартному многоходовому переключателю.

Он передает выбранный вход напрямую на единственный выход.Типичное использование – выбор нового входного значения для триггера из

набор из нескольких альтернатив. В демонстрационных целях вводы данных мультиплексоров

не все связаны со статическими входными значениями,

но также и к двум генераторам часов с разными периодами синхронизации.

Это должно позволить вам напрямую «видеть», какой входной сигнал

передается мультиплексором. Демультиплексор выполняет функцию, обратную мультиплексору. Он передает значение на одном входе данных выбранному.

из его нескольких выходов. Он передает значение на одном входе данных выбранному.

из его нескольких выходов. |

[PDF] 8-битный линейный мультиплексор 4 в 1

1 Проект Часть I Спецификация 8-битного линейного мультиплексора 4-к-1: В этом разделе проекта описывается конструкция 4-к -…

Часть проекта I, спецификация 8-битного линейного мультиплексора 4-к-1: В этом разделе проекта описывается конструкция мультиплексора 4-к-1, который принимает две 8-битные шины в качестве входов и производит одну 8-битную шину в качестве выходных. . Мультиплексор (MUX) – это комбинационная схема, которая использует входы выбора для выбора двоичной информации из нескольких входов и направляет ее на один выход (Mano and Kime, 149).Формулировка и оптимизация: логическое выражение для линейного мультиплексора 4-к-1 выглядит следующим образом: Y = ~ S1 ~ S0I0 + ~ S1S0I1 + ~ S1 ~ S0I2 + S1S0I3 Затраты на вход затвора для реализации этого выражения равны 18. Традиционно, это уравнение разложено на множители, чтобы построить несколько иную реализацию мультиплексора. Хотя стоимость ввода-вывода второго выражения выше на 22, эта реализация облегчает расширение схемы для включения большего количества вводов (Mano and Kime, 151). Факторизованное выражение выглядит следующим образом: Y = (~ S1 ~ S0) I0 + (~ S1S0) I1 + (S1 ~ S0) I2 + (S1S0) I3 Полная таблица истинности для линейного мультиплексора 4: 1 состоит из 16 ряды.В сокращенной версии, приведенной в таблице 1, показаны возможные значения для переменных-селекторов S1 и S0 и соответствующей входной переменной I, выбранной для передачи данных. Для выбранной строки ввода вывод будет равен значению ввода (Mano and Kime, 150). S1

Традиционно, это уравнение разложено на множители, чтобы построить несколько иную реализацию мультиплексора. Хотя стоимость ввода-вывода второго выражения выше на 22, эта реализация облегчает расширение схемы для включения большего количества вводов (Mano and Kime, 151). Факторизованное выражение выглядит следующим образом: Y = (~ S1 ~ S0) I0 + (~ S1S0) I1 + (S1 ~ S0) I2 + (S1S0) I3 Полная таблица истинности для линейного мультиплексора 4: 1 состоит из 16 ряды.В сокращенной версии, приведенной в таблице 1, показаны возможные значения для переменных-селекторов S1 и S0 и соответствующей входной переменной I, выбранной для передачи данных. Для выбранной строки ввода вывод будет равен значению ввода (Mano and Kime, 150). S1S0

Y

0

0

I0

0

1

I1

1

0

I2

1

1

I3

Таблица 1: 4-to -1 Линейный мультиплексор Краткая таблица истинности

Реализация линейного мультиплексора 4-к-1 показана на рисунке 1. Конструкция состоит из декодера с 2 на 4 строки на левой стороне с двумя однобитными входами выбора, S1 и S0. Четыре входа – это 8-канальные шины I0, I1, I2 и I3. Схема И-ИЛИ в правой части схемы разбита на подсхемы, часть И и часть ИЛИ. Подконструкция каждой схемы импортируется иерархически, чтобы сохранить ясность и организацию комбинационной схемы.

Конструкция состоит из декодера с 2 на 4 строки на левой стороне с двумя однобитными входами выбора, S1 и S0. Четыре входа – это 8-канальные шины I0, I1, I2 и I3. Схема И-ИЛИ в правой части схемы разбита на подсхемы, часть И и часть ИЛИ. Подконструкция каждой схемы импортируется иерархически, чтобы сохранить ясность и организацию комбинационной схемы.

Рисунок 1: Линейный мультиплексор 4-к-1 с двумя 8-битными входами шины и одним 8-битным выходом шины

Подконструкция схемы логического элемента AND показана на рисунке 2.Входная 8-битная шина B8i разделяется на отдельные биты с помощью расширителя. Затем каждый бит проходит через логический элемент И вместе с сигналом селектора S. Выходы каждого логического элемента И затем объединяются в единую 8-битную шину.

Рисунок 2: 8-битная шина и схема

Подконструкция логической схемы логического элемента ИЛИ показана на рисунке 3. Четыре 8-битных входа шины расширены до отдельных битов. Четыре бита с одной и той же позицией, каждый из которых происходит от другой 8-битной шины, проходят через логический элемент ИЛИ, а затем выход снова объединяется в 8-битную шину.

Рисунок 3: 8-битная шина ИЛИ Цепь

Проверка: Чтобы проверить функциональность 8-битного мультиплексора 4-к-1, необходимо сначала протестировать два подкомпонента. Подконструкция AND проверяется установкой селектора S сначала равным 0, а затем равным 1. Когда сигнал селектора равен 0, выход всегда также равен 0. Когда сигнал селектора равен 1, схема И включена, и каждый из 8 битов проходит через логический элемент И. Когда битовое входное значение 8-

установлено на 0, выходное значение также равно 0 для каждого бита.Когда для каждого из восьми битов установлено значение 1 (11111111 в двоичном формате или 255 в десятичном), то выходной сигнал также равен 255 в десятичном формате. Форма сигнала на рисунке 4 (n0 – вход, n1 – селектор, n18 – выход) иллюстрирует этот тест.

Рисунок 4: Форма сигнала вспомогательной схемы логического элемента И

Затем проверяется вспомогательная схема ИЛИ, устанавливая каждый бит равным 1 в каждом 8-битном входе шины, в то время как остальные три входные шины устанавливаются на 0. Этот тест проиллюстрирован в форме сигнала на рисунке 5 (n0 – это B8i0, n1 – это B8i1, n2 – это B8i2, n3 – это B8i3, а n44 – это B8o).

Этот тест проиллюстрирован в форме сигнала на рисунке 5 (n0 – это B8i0, n1 – это B8i1, n2 – это B8i2, n3 – это B8i3, а n44 – это B8o).

Рисунок 5: Форма сигнала вспомогательной конструкции логического элемента ИЛИ

Полный 8-битный линейный мультиплексор 4 к 1 тестируется путем проверки каждой возможной комбинации входов селекторных входов S1 и S0, как показано в таблице истинности в таблице 1. Этот тест проиллюстрирован осциллограммой на Рисунке 6 (n0 – S1, n2 – S0, а n16 – Y)

Рисунок 6: 8-битный сигнал линейного мультиплексора 4 к 1

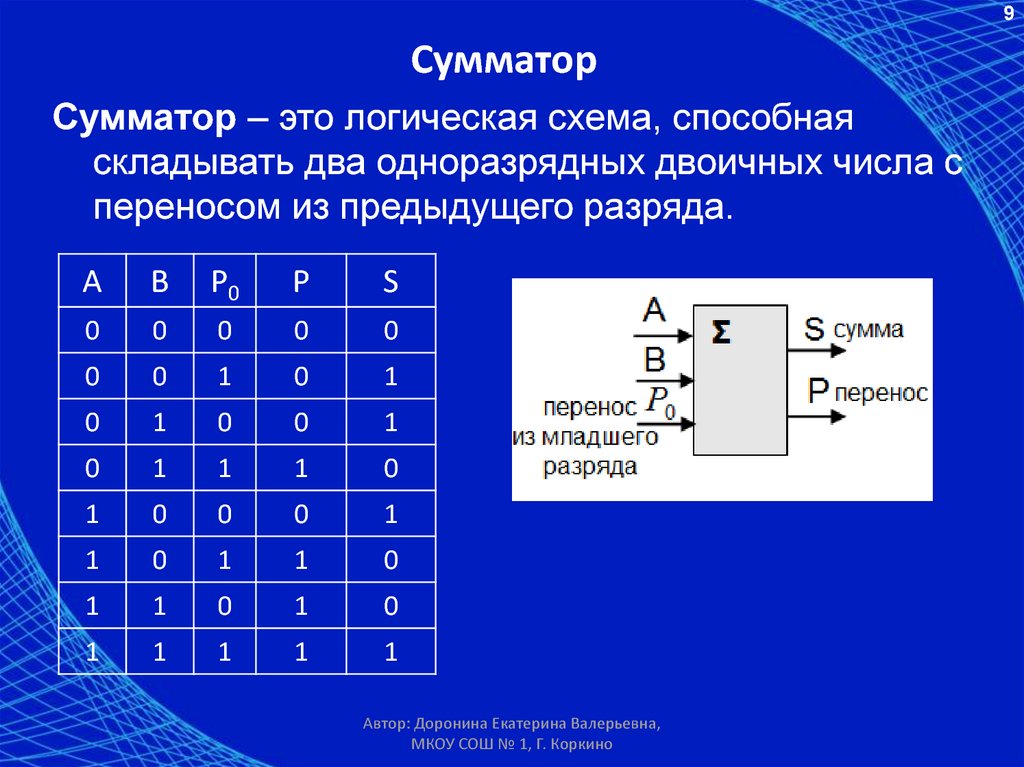

8-битный сумматор Спецификация: этот раздел проекта описывается конструкция 8-битного сумматора. Сумматор – это арифметическая комбинационная схема, которая выполняет операцию сложения заданного числа.(Mano and Kime, 169) Формулировка и оптимизация: 8-битный сумматор построен с использованием восьми полных сумматоров, каждый из которых выполняет сложение трех входных битов. Булевы выражения для суммы (S) и переноса (C) полного сумматора следующие: S = (XY) ZC = XY + Z (XY) Полная таблица истинности для полного сумматора показана в таблице 2 ( Мано и Кимэ, 170). X

X

Y

Z

C

S

0

0

0

0

0

0

0

1

0

1

0

1

0

0

1

0

1

1

1

0

1

0

0

0

1

1

0

1

1

0

1

1

0

1

0

1

1

1

1

1

Таблица 2: Таблица истинности полного сумматора

Реализация полного сумматора , показанный на рисунке 7, состоит из двух однобитовых входов, A и B, и входа переноса Ci.Выходы представляют собой сумму S и перенос Co. Как показывает таблица истинности, когда оба входных бита равны 1, выходное значение суммы равно 0, а выходное значение переноса содержит 1.

Рисунок 7: Полный сумматор

Функция переноса полного сумматора позволяет сложить несколько битовых чисел. В 8-битном сумматоре (рис. 8) используются восемь подконструкций полных сумматоров, соединенных в цепочку. Выходной сигнал переноса одного полного сумматора соединяется с входом переноса следующего сумматора, образуя сумматор переноса с пульсацией.Два 8-битных входа шины, A и B, расширяются до одиночных битов и подключаются к соответствующему полному сумматору, соответствующему положению бита. Ci для полного сумматора младшего разряда устанавливается в 0. Выходной сигнал переноса сумматора старшего разряда равен Co (Mano and Kime, 172). Иерархический дизайн за счет использования полных подкомпонентов сумматора помогает поддерживать организацию всей принципиальной схемы.

8) используются восемь подконструкций полных сумматоров, соединенных в цепочку. Выходной сигнал переноса одного полного сумматора соединяется с входом переноса следующего сумматора, образуя сумматор переноса с пульсацией.Два 8-битных входа шины, A и B, расширяются до одиночных битов и подключаются к соответствующему полному сумматору, соответствующему положению бита. Ci для полного сумматора младшего разряда устанавливается в 0. Выходной сигнал переноса сумматора старшего разряда равен Co (Mano and Kime, 172). Иерархический дизайн за счет использования полных подкомпонентов сумматора помогает поддерживать организацию всей принципиальной схемы.

Рисунок 8: 8-битный сумматор

Проверка: Для проверки функциональности полного подкомпонента сумматора достаточно протестировать только один экземпляр схемы.Поскольку 8-битный сумматор построен с использованием восьми точных копий вспомогательной схемы, когда доказано, что одна копия работает правильно, все остальные также считаются правильными. Проверка полной функциональности сумматора проверяет каждую из восьми возможных входных комбинаций, как указано в таблице истинности (Таблица 2). Форма сигнала для этого теста (n0 – A, n1 – B, n7 – Ci, n6 – S, а n3 – Co) показана на рисунке 6.

Проверка полной функциональности сумматора проверяет каждую из восьми возможных входных комбинаций, как указано в таблице истинности (Таблица 2). Форма сигнала для этого теста (n0 – A, n1 – B, n7 – Ci, n6 – S, а n3 – Co) показана на рисунке 6.

Рисунок 6: Полная форма сигнала сумматора

Ссылки Мано, Моррис М. и Чарльз Р.Кимэ. Основы логики и компьютерного дизайна. 4-е изд. Аппер-Сэдл-Ривер, Нью-Джерси: Pearson Education, Inc. 2008.

Построить мультиплексор 4: 1 с использованием логических вентилей

Мультиплексор – это комбинационная схема (это тип схемы, выход которой зависит от заданных входов с использованием различных логических вентилей) который принимает несколько входов и обеспечивает только один выход. Он состоит из строк входных данных, строк выбора и единственного выхода.

Чтобы построить мультиплексор 4 к 1, нам нужно знать, сколько строк выбора нам потребовалось для создания мультиплексора?

Нам требуется n строк выбора, где 2 n представляет общее количество входных строк, а n представляет строки выбора. (В данном случае 2 2 , что дает 4 строки ввода и 2 строки выбора).

(В данном случае 2 2 , что дает 4 строки ввода и 2 строки выбора).

Мультиплексор часто обозначается сокращенно как MUX, или «многие к одной цепи», или «параллельно» к последовательной цепи.

Это селектор данных, который обеспечивает механизм для выбора одной двоичной информации из многих входных линий и передачи ее на выходную линию

Преимущества мультиплексора: –

- Это менее затратно и снижает сложность схемы передачи

- Это может использоваться для реализации многих комбинационных схем

- Это уменьшает количество проводов

Применения мультиплексора:

- Он используется в системе связи i.e Спутниковые системы, телефонные сети

- Он используется для чтения данных из ячеек памяти в памяти компьютера

Типы мультиплексоров

Существуют различные типы мультиплексоров, некоторые из которых приведены ниже:

- 2: 1 MUX

- 4: 1 MUX

- 8: 1 MUX

- 16: 1 MUX

- 32: 1 MUX

В этой статье мы обсудим 4: 1 MUX.

Вот шаги для разработки или создания мультиплексора 4: 1 или мультиплексора 4: 1 с использованием логических вентилей:

1) Теперь создайте схему мультиплексора с 4 входными линиями, 2 линиями выбора и 1 выходом.На диаграмме ниже A 0 , A 1 , A 2 и A 3 – это строки входных данных, S 0 и S 1 – это строки выбора и, наконец, одна строка вывода с именем Y.

2) Так выглядит таблица истинности для 4 к 1 MUX. Согласно таблице истинности, выход мультиплексора полностью зависит от строк выбора (двоичные данные, 00,01,10 и 11), и один вход будет выбран из всех строк входных данных в качестве выхода.

Таблица истинности

| Линии выбора | Выход | ||||

|---|---|---|---|---|---|

| S 0 | S 66 | 0 | 0 | A 0 | |

| 0 | 1 | A 1 | |||

| 1 | 0 | A 2 | 3 | ||

Вышеупомянутая таблица создается следующим образом:

Если S 0 = 0 и S 1 = 0, то на выходе будет A 0 .

Аналогично, когда S 0 = 0 и S 1 = 1, тогда выходным будет A 1 .

Это можно представить выражением.

Выход = S 0 ‘.S 1 ‘ A 0 + S 0 ‘.S 1 A 1 + S 0 .S 1 ‘ A 2 + S 0 .S 1 A 3

3) На последнем этапе спроектируйте мультиплексор 4 к 1, используя 4 логических элемента И и один логический элемент ИЛИ.

Пояснение:

На диаграмме выше было две строки выбора с соответствующими дополнениями, использующими инверторы.Каждый вентиль И содержал три входа из S 1 , S 0 и конкретный вход A. наконец, выходы всех вентилей И стали входом для логического элемента ИЛИ и обеспечивали один выход.

СвязанныеМультиплексор и демультиплексор 4-к-1 в современной электронике

Мультиплексор

A Мультиплексор – это

схема с множеством входов, но только с одним выходом. Мультиплекс означает много в

один. Мультиплексор еще называют

как Mux .Применяя управляющие сигналы, мы можем направить любой вход на

выход. Таким образом, он также называется селектором данных, а управляющие входы называются

выберите входы.

Мультиплекс означает много в

один. Мультиплексор еще называют

как Mux .Применяя управляющие сигналы, мы можем направить любой вход на

выход. Таким образом, он также называется селектором данных, а управляющие входы называются

выберите входы.

Схема имеет n входных сигналов, m сигналов управления и 1 выходной сигнал. Обратите внимание, что m управляющих сигналов можно выбрать максимум 2 m входов. сигналы, таким образом, n <2 м .

| Блок-схема мультиплексора n-to-1 |

Мультиплексор 4-к-1

Мультиплексор 4 к 1 содержит 4 входных бита, 1 выходной бит и 2 управляющих бита.Четыре входных бита: D 0 , D 1 , D 2 и D 3 ,

соответственно; только один входной бит передается на выход. В

выход «Y» зависит от значения управляющего входа AB. Управляющий бит AB решает

какой бит входных данных должен передавать выходные данные. На следующем рисунке

показывает принципиальную схему мультиплексора 4-к-1 с использованием логических элементов И. Например, когда

управляющие биты AB = 00, тогда разрешены более высокие логические элементы И, оставаясь

И ворота ограничены.Таким образом, ввод данных D 0 равен

передается на выход «Y».

Управляющий бит AB решает

какой бит входных данных должен передавать выходные данные. На следующем рисунке

показывает принципиальную схему мультиплексора 4-к-1 с использованием логических элементов И. Например, когда

управляющие биты AB = 00, тогда разрешены более высокие логические элементы И, оставаясь

И ворота ограничены.Таким образом, ввод данных D 0 равен

передается на выход «Y».

| Мультиплексор 4-к-1 |

Если управляющий вход изменен на 11, то все

ворота ограничены, кроме нижних ворот И. В этом случае на выход передается D 3 и Y = D 0 . Если управляющий вход изменен на AB = 11, все ворота

отключены, кроме нижнего вентиля И. В этом случае на выход передается D 3 и Y = D 3 .Лучшим примером мультиплексора 4-к-1 является IC 74153.

В этой ИС выход такой же, как и вход. Еще один пример 4-к-1

мультиплексор IC 45352. В этой IC выход является дополнением

Вход. Принципиальная схема мультиплексора 4-в-1 представлена на рис.

В этой IC выход является дополнением

Вход. Принципиальная схема мультиплексора 4-в-1 представлена на рис.

| Мультиплексор 4-к-1 |

| Таблица истинности |

эта схема имеет следующий вид:

Y = A’B’D 0 + A’BD 1 + AB’D 2 + ABD 3

Понятно, даст СОП представление, каждый вентиль И генерирует термин продукта, который, наконец, Суммируется воротами OR.

Демультиплексор

А демультиплексор – устройство, имеющее одну входную и несколько выходных линий, которые

используется для отправки сигнала на одно из различных устройств. Демультиплекс означает один

во многие. Применяя управляющие сигналы, мы можем направить входной сигнал на один из

выходные линии. Наиболее заметное различие между мультиплексором и демультиплексор состоит в том, что мультиплексор принимает два или много сигналов и кодирует

их по проводу, тогда как демультиплексор меняет то, что делает мультиплексор.

Наиболее заметное различие между мультиплексором и демультиплексор состоит в том, что мультиплексор принимает два или много сигналов и кодирует

их по проводу, тогда как демультиплексор меняет то, что делает мультиплексор.

| Блок-схема демультиплексора 1 к n |

Демультиплексор 1 к 4

г. Демультиплексор с 1 на 4 содержит 1 входной бит, 4 выходных бита и 2 управляющих бита. Принципиальная схема демультиплексора с 1 на 4 показана ниже.

| Демультиплексор от 1 до 4 |

Входной бит считается Data D.Эти данные

бит передается в бит данных выходных линий, который зависит от AB

значение и управляющий вход. Когда

управляющий вход AB = 01, верхний второй логический элемент И разрешен, в то время как

остальные ворота И ограничены. Таким образом, только бит данных D передается в

выход и Y 1 = Данные.

Таким образом, только бит данных D передается в

выход и Y 1 = Данные.

Если бит данных D низкий, выход Y 1 низкий. Если бит данных D высокий, выход Y 1 высокий. Значение выход Y 1 зависит от значения бита данных D, остальные выходы в низком состоянии.Если управляющий вход изменится на AB = 10, то все ворота ограничены, кроме третьего И ворот из Топ. Тогда бит данных D передается только на выход Y 2 ; и Y 2 = Данные. Лучший пример от 1 до 4 демультиплексор IC 74155.

Читайте также

Селекторы и мультиплексоры данных

- Изучив этот раздел, вы сможете:

- Распознавать использование схем выбора данных и мультиплексора.

- Понимание работы схем выбора данных и мультиплексора.

- • Схемы выбора основных данных (мультиплексора).

- • Мультиплексирование

- • Демультиплексирование

- Ознакомьтесь с работой многобитовых мультиплексоров.

- • Адрес

- Access Multiplexer IC Datasheets.

- Моделируйте работу схемы с помощью программного обеспечения.

Рис 4.2.1 Механические селекторные переключатели

Простым способом соединения нескольких источников информации в аналоговых электронных системах является использование механических переключателей, таких как те, что показаны на рис. 4.2.1. В примере (а) однополюсный двухпозиционный переключатель используется для выбора входа A или входа B для подключения к выходу X. Пример (b) показывает поворотный селекторный переключатель, который может мультиплексировать любой из восьми входов в один выход.

В цифровой электронике выбор нескольких источников данных может выполняться схемами комбинационной логики.Логические сигналы, подаваемые на один или несколько входов выбора данных, инициируют выбор данных, которые могут быть устойчивыми логическими уровнями или целыми потоками цифровой информации. Переключение цифровых сигналов таким образом происходит намного быстрее и надежнее, чем при использовании механических переключающих контактов. Таким образом, селекторы и мультиплексоры цифровых данных являются жизненно важной частью многих цифровых систем. Имена «селектор данных» и «мультиплексор» обычно меняются местами, при этом мультиплексоры называются селекторами данных и наоборот. Если есть какая-либо разница, схему, выбирающую между двумя входами, можно назвать селектором данных, а более сложные схемы, объединяющие несколько входов в один выход, используя различные методы и существующие как в цифровой, так и в аналоговой формах, будут называться мультиплексорами.

Переключение цифровых сигналов таким образом происходит намного быстрее и надежнее, чем при использовании механических переключающих контактов. Таким образом, селекторы и мультиплексоры цифровых данных являются жизненно важной частью многих цифровых систем. Имена «селектор данных» и «мультиплексор» обычно меняются местами, при этом мультиплексоры называются селекторами данных и наоборот. Если есть какая-либо разница, схему, выбирающую между двумя входами, можно назвать селектором данных, а более сложные схемы, объединяющие несколько входов в один выход, используя различные методы и существующие как в цифровой, так и в аналоговой формах, будут называться мультиплексорами.

Схемы выбора основных данных (мультиплексор)

Рис. 4.2.2 Селектор данных

Простой селектор данных, состоящий из одного логического элемента XOR, использовался в схеме 8-битного сумматора / вычитателя, показанной на рис. 4.1.5 и 4.1.6 в модуле 4.1, чтобы изменить функцию схемы от сложения к вычитанию, но это требовалось только для выбора данных B или их обратных B. Схема, показанная на рис. 4.2.2, однако может выбрать любой из два полностью независимых входа данных.

Схема, показанная на рис. 4.2.2, однако может выбрать любой из два полностью независимых входа данных.

Операция, показанная на рис.4.2.2 довольно прост и полагается на «включение» любого из двух вентилей NAND (1 и 2), но не обоих.

Из таблицы истинности для логического элемента И-НЕ, показанной в таблице 4.2.1, можно увидеть, что если на одном из входов (например, вход A) сохраняется логическая 1, то выход будет инверсным по отношению к другому входу. Говорят, что ворота открыты. Если, однако, на входе A сохраняется логический 0, то на выходе всегда будет логическая 1, независимо от состояния второго входа. Таким образом, вентиль отключен, и вход не может достичь выхода, даже в инвертированном виде.Строб 3 на рис. 4.2.2 просто объединяет входы от двух других затворов. Таблица 4.2.2 иллюстрирует работу Рис. 4.2.2.

Мультиплексирование

Управляющий вход (C) схемы на рис. 4.2.2 подается непосредственно на вентиль 1, но инвертируется на вентиль 2. Это гарантирует, что независимо от логического состояния C один вентиль включен, а другой отключен.

Это гарантирует, что независимо от логического состояния C один вентиль включен, а другой отключен.

Следовательно, когда C = 1, элемент И-НЕ 1 будет включен, и его выход будет инверсным входу данных (ieA), и поскольку C (в данном случае логический 0) применяется к управляющему входу элемента 2, его выход будет быть логикой 1.

Применение логического 0 к входу C приведет к отключению логического элемента 1, что сделает его выходную логику 1, а логический элемент 2 будет включен, что приведет к его выходу B.

Таким образом, вентиль 3 всегда будет иметь один из входов, удерживаемых на уровне логической 1, потому что либо вентиль 1, либо вентиль 2 отключен, в то время как другой вход вентиля 3 будет либо A, либо B. Выход вентиля 3 будет инверсным этому входу. , поэтому результат на выходе X будет либо A, либо B в зависимости от состояния линии управления, как видно из таблицы 4.2.2.

Обратите внимание, что эта компоновка из трех вентилей И-НЕ (или четырех, если дополнительный вентиль И-НЕ используется вместо инвертора) работает точно так же, как если инвертор (вентиль НЕ) выбирает любой из двух вентилей И, выходы которых объединяются оператором ИЛИ. вентиль (теорема Де Моргана), но использует только одну интегральную схему с четырьмя входами с 2 входами вместо трех, требуемых решением НЕ / И / ИЛИ.

вентиль (теорема Де Моргана), но использует только одну интегральную схему с четырьмя входами с 2 входами вместо трех, требуемых решением НЕ / И / ИЛИ.

Рис. 4.2.3 Простой демультиплексор

Демультиплексирование

После объединения или мультиплексирования двух источников данных в одну строку вывода обычно в какой-то момент необходимо еще раз разделить или демультиплексировать объединенные данные в отдельные выходные данные.Для этого для схемы на рис. 4.2.2 потребуется схема, подобная показанной на рис. 4.2.3.

Для подключения данных к этому простому демультиплексору требуются два соединения от схемы выбора данных, одно для соединения данных с выхода X схемы выбора данных на рис. 4.2.2 с объединенным входом A / B на рис. 4.2.3 и другое соединение от C на рис. 4.2.2 до C на рис. 4.2.3 для совместного использования управляющего сигнала.

Необходимость использовать две соединительные линии для подключения мультиплексора к демультиплексору для передачи двух сигналов, по-видимому, не оправдывает использование этих двух дополнительных схем, однако принцип мультиплексирования, продемонстрированный на рис. 4.2.2 и 4.2.3 могут быть расширены для мультиплексирования большего количества входных данных, и чем больше линий мультиплексируется таким образом, тем эффективнее становится система. Кроме того, существуют дополнительные способы использования этих методов, помимо передачи данных из одного места в другое, как описано в Модуле цифровой электроники 4.4 (Кодеры и декодеры).

4.2.2 и 4.2.3 могут быть расширены для мультиплексирования большего количества входных данных, и чем больше линий мультиплексируется таким образом, тем эффективнее становится система. Кроме того, существуют дополнительные способы использования этих методов, помимо передачи данных из одного места в другое, как описано в Модуле цифровой электроники 4.4 (Кодеры и декодеры).

Рис. 4.2.4 Мультиплексор 4 в 1

Многобитовые мультиплексоры

Мультиплексоры имеют множество применений.Везде, где необходимо передать несколько сигналов или логических состояний по одному каналу связи, например по проводу, радиоканалу или телефону, используется некоторая форма мультиплексирования. Иногда мультиплексирование и демультиплексирование могут быть очень сложными, гораздо более сложными, чем схема на рисунках 4.2.2 и 4.2.3. В некоторых системах данные передаются на очень большие расстояния, в других, например при передаче данных внутри компьютеров, расстояния могут быть очень короткими. На рис. 4.2.4 показан мультиплексор от 4 до 1, который позволяет передавать 4-битное двоичное число по 3 строкам, одна для данных и две для управления.

На рис. 4.2.4 показан мультиплексор от 4 до 1, который позволяет передавать 4-битное двоичное число по 3 строкам, одна для данных и две для управления.

Адрес

Более крупные мультиплексоры, такие как 4, 8 или 16-битные типы, которые легко доступны в форме IC, используют метод «адресации» конкретного элемента данных с использованием двоичного кода. На рис. 4.2.4 показан мультиплексор 4: 1, в котором для вывода данных с определенного входа один из четырех вентилей NAND с 3 входами должен быть активирован логической 1 на двух его входах, а третий вход должен быть для данных. . Для этого используются две адресные строки, дающие четыре возможных комбинации 1 и 0.Внимательно посмотрите на адресные строки. Когда оба находятся в логическом 0, два инвертора (НЕ вентили) вырабатывают логические единицы на двух входах логического элемента И-НЕ 00. Ни один из других вентилей И-НЕ, адресованных этими линиями, не имеет обоих своих адресных входов на логической 1. Если младший значащий бит (lsb) адреса равен 1, а старший бит (msb) равен 0, тогда включен логический элемент И-НЕ 01. Поскольку две адресные строки могут дать четыре возможных двоичных комбинации, вы должны обнаружить, что, считая сверху, вентиль 00 активируется адресными входами 00 2 , вентиль 01 по адресу 01 2 , вентиль 10 по 10 2 и выход 11 на 11 2 .

Поскольку две адресные строки могут дать четыре возможных двоичных комбинации, вы должны обнаружить, что, считая сверху, вентиль 00 активируется адресными входами 00 2 , вентиль 01 по адресу 01 2 , вентиль 10 по 10 2 и выход 11 на 11 2 .

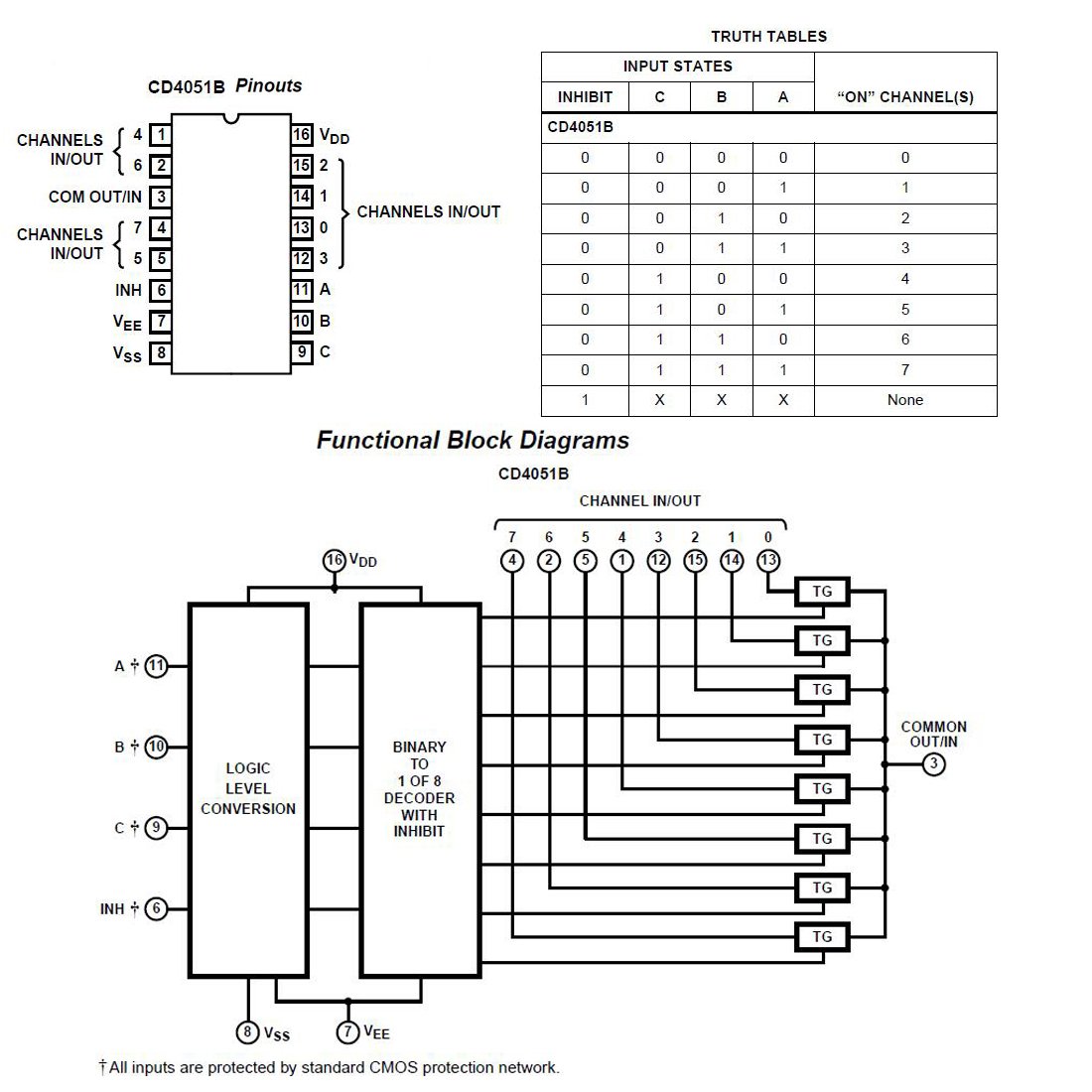

Таблицы данных ИС мультиплексора

Существует множество коммерчески доступных ИС мультиплексоров с множеством дополнительных функций. Ниже приводится список таблиц данных для некоторых базовых мультиплексоров, аналогичных описанным в этой статье.

Обзор D: Компоненты цифровых схем: Вопросы

D1.1.

Нарисуйте две таблицы истинности, иллюстрирующие выходные данные полусумматора, одна таблица для вывода суммы , а другая – для несут выходных данных.

D1.2.

Заполните таблицу истинности справа для следующей схемы. Игнорировать строки, не включенные в таблицу.

D1. 3.

3.

Что касается значений входов и выходов, что отличает полусумматор от полусумматора?

D1.4.

Используя только полусумматоры, покажите, как можно построить полную сумматор. Обязательно пометьте свои входы x , y , и z , а выходы несут и сумма .Также пометьте выходы содержат и сумму для каждого полусумматора.

D1.5.

Используя только полусумматоры и полные сумматоры, изобразите схему, которая принимает шесть входов, представляющих два 3-битных беззнаковых двоичных числа a 2 a 1 a 0 и b 2 b 7 2

1 9069 и который

выдает 4-битный результат с 3 с 2 с 1 с 0 представляющий сумму двух чисел. Обозначьте свой ввод и

выходные провода.

Обозначьте свой ввод и

выходные провода.

D1.6.

Используя только четырехбитовые сумматоры, создайте восьмибитовый сумматор. Каждый четырехбитовый сумматор имеет два четырехбитовых входа и один пятибитовый выход. Ваш восьмибитный сумматор должен иметь два восьмибитных входа и один восьмибитный вывод (не беспокойтесь о девятом выходном бите).

D2.1.

Предположим, у нас есть мультиплексор 4 к 1, входы которого d 00 , d 01 , d 10 , d 11 , s 0267 и s 1 .Каков результат каждого из следующих случаи?

| d 00 | d 01 | d 10 | 0с 1 | из | |||||||||||

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | |||||

| 0 | 0 | 1 | 0 | 0 | 0 | ||||||||||

| 0 | |||||||||||||||

| 0 1 | 0 | ||||||||||||||

| 0 | 1 | 1 | 1 | 1 | 1 | ||||||||||

| 1 | 1 | 0 | 1 | 0 | 1 | ||||||||||

| 1 | 1 | 1 | 0 | 1 |

| 1. | D изменяется на 1. |

| 2. | ck изменяется на 1. |

| 3. | D изменяется на 0. |

| ck изменяется на 0. | |

| 5. | ck изменяется на 1. |

| 6. | D изменяется на 1. |

D3.6.

Схема ниже включает два D-триггера.

Напомним, что сохраненное состояние D-триггера остается неизменным, пока

как установите = 0. В тот момент, когда установит, переключится на 1,

его сохраненный бит переключается на значение , и он сохраняет это значение

пока не установит, что снова изменится на 1.

В тот момент, когда установит, переключится на 1,

его сохраненный бит переключается на значение , и он сохраняет это значение

пока не установит, что снова изменится на 1.

Допустим, пользователь вводит последовательность входных данных, указанную в таблице справа, один за другим.Обозначьте результат схема будет устанавливаться после каждого ввода пользователя.

a b c o 1 1 0 1 1 ? 0 0 1 ? 0 0 0 ? 0 1 0 ? 0 0 0 ? 1 0 0 ?

D3. 7.

7.

Предположим, что верхний D-триггер в приведенной ниже схеме держит 1 а нижний D-триггер держал 0, в то время как вход x был 0. Затем кто-то переключает x введите пять раз (до 1, затем 0, затем 1, затем 0, затем 1). Заполните таблицу, чтобы показать, как будут выглядеть выходные значения. изменение.

D4.1.

Мы рассмотрели приведенную ниже схему реализации счетчика турникета.Как бы вела себя эта схема, если бы мы использовали D-защелки (срабатывание по уровню) вместо D-триггеров (срабатывание по фронту)?

D4.2.

Используя мультиплексор 2-к-1 и D-триггер, постройте

схема, имеющая один выход и три входа Т , Х ,

и ск .

Выходной сигнал схемы должен оставаться на одном и том же значении независимо от

входы, до момента, когда ck изменится с 0 на 1. В то время, если T равно 1, выход схемы должен переключиться на свое

противоположное значение; и если T равен 0, выход должен измениться на

значение X в этот момент.

В то время, если T равно 1, выход схемы должен переключиться на свое

противоположное значение; и если T равен 0, выход должен измениться на

значение X в этот момент.

Примечание: Не используйте логические вентили. Напомним, что D триггер имеет выходы Q и Q .

D4.3.

Используя два D-триггера и простые логические элементы (И / ИЛИ / НЕ), построить схему, выход которой равен 1 на каждом четвертом такте. То есть, когда выход равен 1, выход должен измениться на 0 для следующие три раза часы перейдут с 0 на 1, затем повернутся к 1 в четвертый раз, затем цикл повторяется.

D4.4.

Используя только логические элементы И, ИЛИ и НЕ в дополнение к двум D-триггерам, постройте

схема с одним входом, двухбитовый выход которой каждый раз изменяется следующим образом

его единственный вход повышается с 0 до 1:

Когда вывод 01 (2) , он меняется на 10 (2) ;

когда на выходе будет 10 (2) , он изменится на 11 (2) ;

а когда на выходе будет 11 (2) , он изменится на 01 (2) . (Это может быть полезно для управления светофором.)

D4.5.

Предположим, у меня есть восемь триггеров, пронумерованных от 0 до 7, и у меня есть 3-битный адрес памяти, указывающий, какой бит триггера я хочу получить. Какой компонент будет полезен для извлечения бита из соответствующего триггера?

D1.1.

D1.2.

| a | b | c | x | y | |

| 0 | 0 | ||||

| 1 | 0 | 1 | 1 | 1 | |

| 1 | 1 | 0 | 1 | 1 | |

| 1 | 0003 11 |

D1.3.

Полусумматор имеет два входа и выводит сумму этих двух битов,

в то время как полный сумматор имеет три входа и выводит сумму этих трех

биты.

D1.4.

D1.5.

D1.6.

Конструкция этой схемы аналогична конструкции полный сумматор с использованием полусумматора.

D2.1.

| d 00 | d 01 | d 10 | 0с 1 | из | |||||||||||

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | ||

| 0 | 0 | 1 | 0 | 0 | 0 | 000 0 | 000 0 | 000 0 | 1 | 1 | 0 | 0 | |||

| 0 | 1 | 1 | 1 | 1 | 900 03 11 | ||||||||||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | |||||||||

| 1 | 1 | 1 | 0004000 0

D2. 2.

2.

Демультиплексор с 1 на 4 имеет три входа, включая вход данных и два входа выбора, представляющие два бита числа и . Он имеет четыре выхода, номера от 00 (2) до 11 (2) . Демультиплексор направляет свои входные данные на выход, номер которого с ; значения остальных выходов будут 0.

D2.3.

D2.4.

D2.5.

D3.1.

В комбинационной схеме выход может полностью определяться текущей комбинацией входов.В последовательной схеме выход также может зависеть от последовательности предыдущих входов.

D3.2.

D3.3.

В устройстве с синхронизацией по фронту значение изменяется только в этот момент

что тактовый сигнал становится равным 1. При срабатывании уровня

устройство, однако, значение памяти продолжает принимать любые значения

задано, пока его набор , вход равен 1. (Например, в

D-триггер, если вход изменяется, а часы остается 1, запомненное значение не меняется. Однако в защелке

изменение ввода D , в то время как устанавливает равным 1, приводит к

изменение запомненного значения.)

Однако в защелке

изменение ввода D , в то время как устанавливает равным 1, приводит к

изменение запомненного значения.)

D3.4.

Пока ck равно 0, второй защелки устанавливает input равен 0, поэтому его значение и его выход остаются неизменными. Однако для первой защелки значение на входе равно 1, и поэтому значение первой защелки постоянно обновляется до значения D . Когда ck изменяется на 1, первой защелки устанавливает вход изменяется на 0, поэтому значение защелки фиксируется на значении D в то время, когда ck изменилось на 1.Между тем, когда ck становится 1, второй фиксатор устанавливает вход изменяется на 1, и поэтому он начинает устанавливать значение защелки на свое data input – значение D в то время, когда ck стало 1, как хранится в первой защелке.

D3.5.

На шаге 2 значение D-триггера меняется на 1. На шаге 5 он меняется на 0.

На шаге 5 он меняется на 0.

D3.6.

| a | b | c | o | |||||||||

| 1 | 1 | 1 | 1 | |||||||||

| 0 | 0 | 1 | 1 | |||||||||

| 0 | 0 | 0 | 1 | |||||||||

| 0 | 0003 | 1 | 1 0 | 0 | 0 | 0 | ||||||

| 1 | 0 | 0 | 1 |

D3.7.

D4.1.

На время, пока кто-то находится в луче ( из равно 1), защелки обновят свои входы данных . В

новые значения будут переданы в сумматор, который вернется в данных входов, для повторного обновления защелок и

снова и снова. Следствием этого является то, что счетчик считается как

как можно быстрее, пока кто-то находится в луче света; однажды

человек выходит из луча, итоговое значение выросло на

намного больше 1, увеличиваясь на непредсказуемую величину.

(На самом деле, поскольку разные выходы сумматора имеют разные глубины, и поскольку неизбежно будут различия в том, как в любом случае быстро обновляются транзисторы, поведение даже больше беспорядочный, чем просто очень быстрый подсчет: некоторые защелки будут обновляться чаще, чем другие защелки.)

D4.2.

D4.3.

D4.4.

D4.5.

Нам нужен мультиплексор 8: 1, где выход каждого триггера подключен к одному из индексированных входов мультиплексора, а биты адреса подключены к входам выбора мультиплексора.

Лаборатория подачи воздуха – EE4480-Lab 04: Разработка 4-битного ALU и его реализация в FPGA

1-битный полный сумматор