Vt1 транзистор

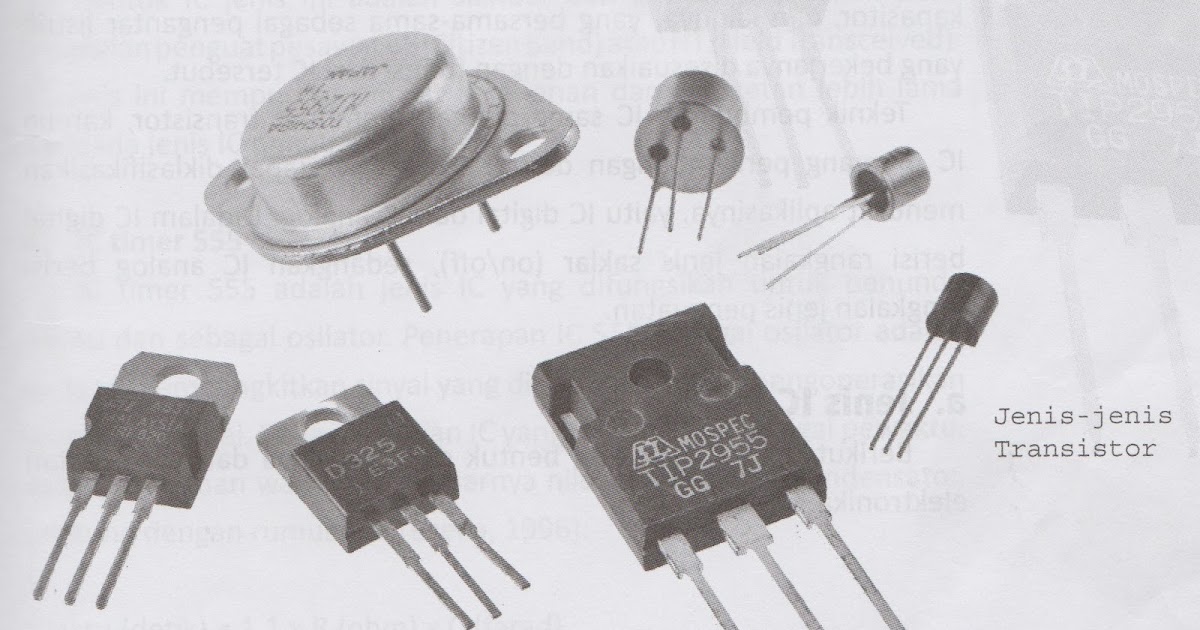

Транзисторы — это полупроводниковые приборы, которые предназначены для усиления, генерации и преобразования электрических сигналов. Это главный компонент в любой электрической схеме. Транзисторы бывают полевые и биполярные. Отличие их в том, что в биполярном транзисторе в переносе заряда участвуют электроны носители отрицательных зарядов и дырки носители положительных зарядов , а в полевом — один из носителей зарядов электроны или дырки.

Поиск данных по Вашему запросу:

Схемы, справочники, даташиты:

Прайс-листы, цены:

Обсуждения, статьи, мануалы:

Дождитесь окончания поиска во всех базах.

По завершению появится ссылка для доступа к найденным материалам.

Содержание:

- 19) Составной транзистор

- Условное обозначение транзисторов на схемах

- Триггер на транзисторах

- Составной транзистор (схема Дарлингтона)

- Составные транзисторы.

Схемы включения.

- ЗАМЕНА ТРАНЗИСТОРА ДАРЛИНГТОНА ПОЛЕВЫМИ ТРАНЗИСТОРАМИ – СДЕЛАЙ САМ

- Составной транзистор дарлингтона работа и устройство

ПОСМОТРИТЕ ВИДЕО ПО ТЕМЕ: Diode Transistor Logic Gates

19) Составной транзистор

Регистрация Вход. Ответы Mail. Вопросы – лидеры Квадрокоптер летит токо в верх модель YH 1 ставка. Не взлетает квадрокоптер 1 ставка. Перестал работать Mi band 4 1 ставка. А разве понятие “эфир” можно всерьёз рассматривать в электронике? Задача по физике 1 ставка. Лидеры категории Антон Владимирович Искусственный Интеллект.

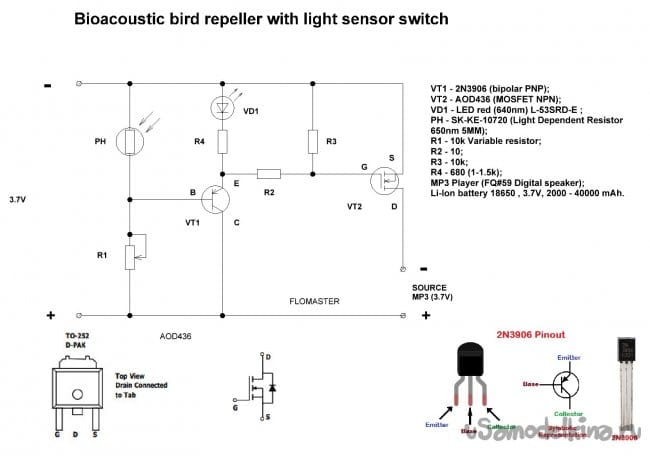

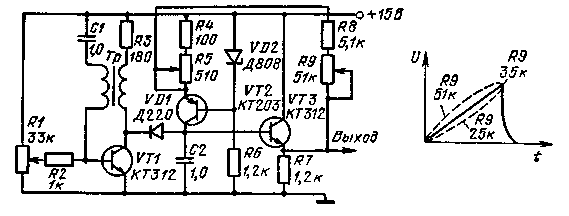

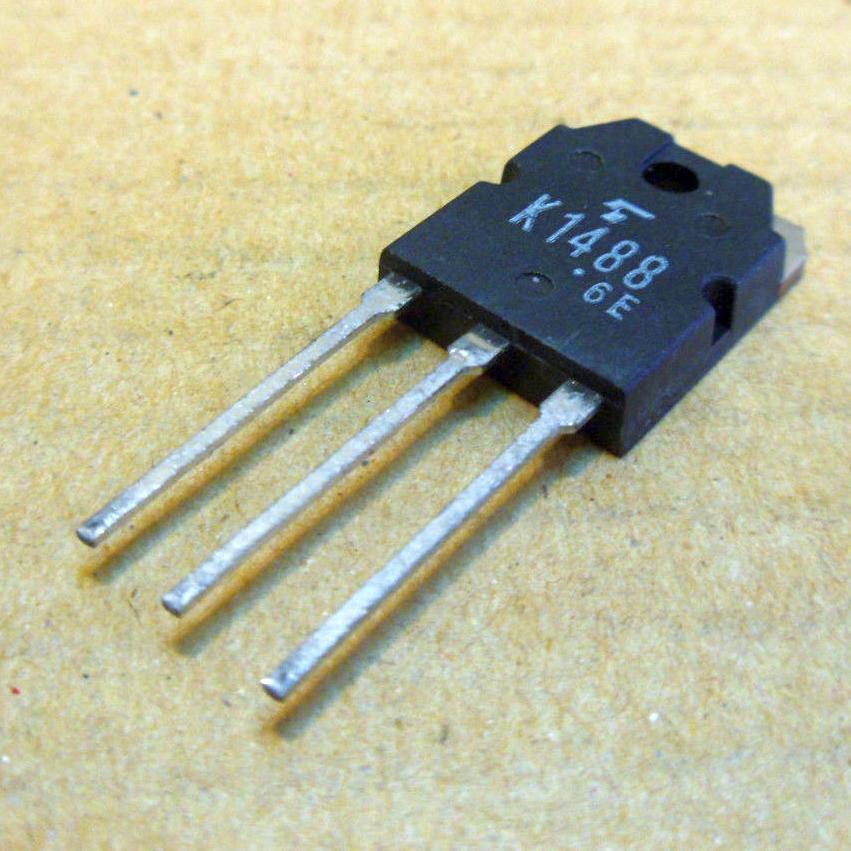

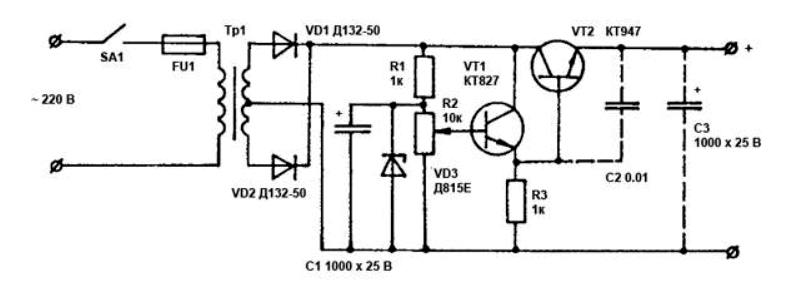

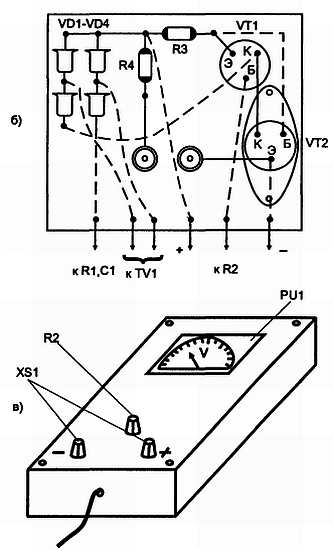

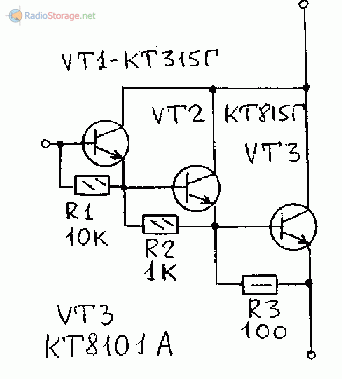

Кислый Высший разум. Голосование за лучший ответ. Nik Vas Искусственный Интеллект 2 года назад Все три транзистора являются усилителями низкой частоты. Комментарий удален IF Мастер помогите пожалуйста найти эту схему в журнале радио в каком выпуске какого года содержится эта схема. Комментарий удален happy case Мудрец сзр. Юрий Ладога Просветленный 2 года назад все три усилители, можно сказать vt1 – входящий, vt2 и vt3 – оконечный.

Комментарий удален IF Мастер помогите пожалуйста найти эту схему в журнале радио в каком выпуске какого года содержится эта схема. Комментарий удален happy case Мудрец сзр. Юрий Ладога Просветленный 2 года назад все три усилители, можно сказать vt1 – входящий, vt2 и vt3 – оконечный.

Вольный ветер Искусственный Интеллект 2 года назад Схема слишком много потребляет питания, батарейки на час не хватит, найди более экономичную Комментарий удален Вольный ветер Искусственный Интеллект Громкоговорящее устройство автобуса, схема простая довольно мощная и экономичная Похожие вопросы. Также спрашивают.

Условное обозначение транзисторов на схемах

Транзистор от английских слов transfer — переносить и re sistor — сопротивление — полупроводниковый прибор, предназначенный для усиления, генерирования и преобразования электрических колебаний. Наиболее распространены так называемые биполярные транзисторы. Электропроводность эмиттера и коллектора всегда одинаковая p или n , базы — противоположная n или p. Иными словами, биполярный транзистор содержит два р-n-перехода: один из них соединяет базу с эмиттером эмиттерный переход , другой — с коллектором коллекторный переход. Буквенный код транзисторов — латинские буквы VT.

Иными словами, биполярный транзистор содержит два р-n-перехода: один из них соединяет базу с эмиттером эмиттерный переход , другой — с коллектором коллекторный переход. Буквенный код транзисторов — латинские буквы VT.

Транзисторы — это полупроводниковые приборы, которые предназначены для усиления, генерации и преобразования электрических сигналов.

Триггер на транзисторах

На фото справа вы видите первый работающий транзистор, который был создан в году тремя учёными — Уолтером Браттейном, Джоном Бардином и Уильямом Шокли. Несмотря на то, что первый транзистор имел не очень презентабельный вид, это не помешало ему произвести революцию в радиоэлектронике. Транзистор является первым твёрдотельным устройством, способным усиливать, генерировать и преобразовывать электрический сигнал. Он не имеет подверженных вибрации частей, обладает компактными размерами. Это делает его очень привлекательным для применения в электронике. Это было маленькое вступление, а теперь давайте разберёмся более подробно в том, что же представляет собой транзистор. Сперва стоит напомнить о том, что транзисторы делятся на два больших класса. К первому относятся так называемые биполярные, а ко второму — полевые они же униполярные.

Сперва стоит напомнить о том, что транзисторы делятся на два больших класса. К первому относятся так называемые биполярные, а ко второму — полевые они же униполярные.

Составной транзистор (схема Дарлингтона)

Составной транзистор транзистор Дарлингтона — объединение двух или более биполярных транзисторовс целью увеличения коэффициента усиления по току. Составной транзистор являетсякаскадным соединениемнескольких транзисторов, включенных по схеме с общим коллектором. Нагрузкой предыдущего каскада является переход база-эмиттер транзистора следующего каскада, то есть транзисторы соединяются коллекторами, а эмиттер входного транзистора соединяется с базой выходного. Кроме того, может использоваться нагрузка в виде резистора. Такое соединение рассматривают как один транзистор, коэффициент усиления по току которого при работе транзисторов в активном режиме приблизительно равен произведению коэффициентов усиления первого и второго транзисторов: Составной транзистор имеет три вывода база, эмиттер и коллектор , которые эквивалентны выводам обычного одиночного транзистора.

Составной транзистор транзистор Дарлингтона — объединение двух или более биполярных транзисторов с целью увеличения коэффициента усиления по току.

Составные транзисторы. Схемы включения.

Войдите , пожалуйста. Хабр Geektimes Тостер Мой круг Фрилансим. Мегапосты: Криминальный квест HR-истории Путешествия гика. Войти Регистрация. Биполярные транзисторы. For dummies Электроника для начинающих Предисловие Поскольку тема транзисторов весьма и весьма обширна, то посвященных им статей будет две: отдельно о биполярных и отдельно о полевых транзисторах.

ЗАМЕНА ТРАНЗИСТОРА ДАРЛИНГТОНА ПОЛЕВЫМИ ТРАНЗИСТОРАМИ – СДЕЛАЙ САМ

При проектировании схем радиоэлектронных устройств часто желательно иметь транзисторы с параметрами лучше тех моделей, которые предлагают фирмы производители радиоэлектронных компонентов или лучше чем позволяет реализовать доступная технология изготовления транзисторов. Эта ситуация чаще всего встречается при проектировании интегральных микросхем. Нам обычно требуются больший коэффициент усиления по току h 21 , большее значение входного сопротивления h 11 или меньшее значение выходной проводимости h Улучшить параметры транзисторов позволяют различные схемы составных транзисторов. Существует много возможностей реализовать составной транзистор из полевых или биполярных транзисторов различной проводимости, улучшая при этом его параметры. Наибольшее распространение получила схема Дарлингтона. В простейшем случае это соединение двух транзисторов одинаковой полярности.

Нам обычно требуются больший коэффициент усиления по току h 21 , большее значение входного сопротивления h 11 или меньшее значение выходной проводимости h Улучшить параметры транзисторов позволяют различные схемы составных транзисторов. Существует много возможностей реализовать составной транзистор из полевых или биполярных транзисторов различной проводимости, улучшая при этом его параметры. Наибольшее распространение получила схема Дарлингтона. В простейшем случае это соединение двух транзисторов одинаковой полярности.

В рассматриваемой конструкции, представляющей собой двухкаскадное радиопередающее устройство, на транзисторе VT1 выполнен микро-.

Составной транзистор дарлингтона работа и устройство

Исследование статических и динамических характеристик КМОП-инвертора. Инвертор реализует функцию НЕ и является простейшим базовым логическим элементом. В качестве инверторов используют ключи на биполярных или полевых транзисторах. Передаточная характеристика инвертора показана на рис.

Составным транзистором называется соединение двух и более транзисторов, эквивалентное одному транзистору, но с большим коэффициентом усиления или другими отличительными свойствами. Известно несколько схем составного транзистора. Схема Дарлингтона. Она характеризуется тем, что входные цепи всех входящих в нее транзисторов соединены последовательно, а выходные цепи — параллельно рис.

Познакомиться с работой различных электронных устройств лучше всего на примере простых транзисторных схем.

Регистрация Вход. Ответы Mail. Вопросы – лидеры Квадрокоптер летит токо в верх модель YH 1 ставка. Не взлетает квадрокоптер 1 ставка. Перестал работать Mi band 4 1 ставка.

В схеме усилительного каскада на рис. Для создания смещения здесь используется делитель напряжения -. В соответствии с выбранным положением начальной рабочей точки, определяемой напряжением смещения, в коллекторной цепи транзистора протекает начальный коллекторный ток. Этот ток создает на эмиттерном сопротивлении падение напряжения:.

Условное обозначение транзисторов на схемах

Транзистор (от английских слов transfer) — переносить и (re)sistor — сопротивление) — полупроводниковый прибор, предназначенный для усиления,

генерирования и преобразования электрических колебаний. Наиболее распространены так называемые

Буквенный код транзисторов — латинские буквы VT. На схемах эти полупроводниковые приборы обозначают, как показано на рис. 1.

Здесь короткая черточка с линией от середины символизирует базу, две наклонные линии, проведенные к ее краям под углом 60°, — эмиттер и коллектор.

Рис.1. Условное обозначение транзисторов

Знать электропроводность эмиттера базы и коллектора необходимо для того, чтобы правильно подключить транзистор к источнику питания. В справочниках эту информацию приводят в виде структурной формулы. Транзистор, база которого имеет электропроводимость типа n, обозначают формулой p-n-p, а транзистор с базой, имеющей электропроводность типа p-n-p. В первом случае на базу и коллектор следует подавать отрицательное по отношению к эмиттеру напряжение, во втором — положительное.

Для наглядности условное графическое обозначение дискретного транзистора обычно помещают в кружок, символизирующий его корпус. Иногда металлический корпус соединяют с одним из выводов транзистора. На схемах это показывается точкой в месте пересечения соответствующего вывода с

символом корпуса. Если же корпус снабжен отдельным выводом, линию-вывод допускается присоединять к кружку без точки (VT3 на рис. 1). В целях повышения

информативности схем рядом с позиционным обозначением транзистора допускается указывать его тип.

Иногда металлический корпус соединяют с одним из выводов транзистора. На схемах это показывается точкой в месте пересечения соответствующего вывода с

символом корпуса. Если же корпус снабжен отдельным выводом, линию-вывод допускается присоединять к кружку без точки (VT3 на рис. 1). В целях повышения

информативности схем рядом с позиционным обозначением транзистора допускается указывать его тип.

Линии электрической связи, идущие от эмиттера и коллектора проводят в одном из двух направлений: перпендикулярно или параллельно выводу базы (VT3-VT5). Излом вывода базы допускается лишь на некотором расстоянии от символа корпуса (VT4).

Транзистор может иметь несколько эмиттерных областей (эмиттеров). В этом случае символы эмиттеров обычно изображают с одной стороны символа базы, а окружность обозначения корпуса заменяют овалом (рис. 1, VT6).

Стандарт допускает изображать транзисторы и без символа корпуса, например, при изображении бескорпусных транзисторов или когда на схеме необходимо показать

транзисторы, входящие в состав сборки транзисторов или интегральной схемы.

Поскольку буквенный код VT предусмотрен для обозначения транзисторов, выполненных в виде самостоятельного прибора, транзисторы сборок обозначают одним из следующих способов: либо используют код VT и присваивают им порядковые номера наряду с другими транзисторами (В этом случае на поле схемы помещают такую, например, запись: VT1-VT4 К159НТ1), либо используют код аналоговых микросхем (DA) и указывают принадлежность транзисторов в сборке в позиционном обозначении (рис. 2, DA1.1, DA1.2). У выводов таких транзисторов, как правило, приводят условную нумерацию, присвоенную выводам корпуса, в котором выполнена матрица.

Рис.2. Условное обозначение транзисторных сборок

Без символа корпуса изображают на схемах и транзисторы аналоговых и цифровых микросхем (для примера на рис. 2 показаны транзисторы структуры n-p-n с тремя и четырьмя эмиттерами).

Условные графические обозначения некоторых разновидностей биполярных транзисторов получают введением в основной символ специальных знаков. Так, чтобы изобразить лавинный транзистор, между символами эмиттера и коллектора помещают знак эффекта лавинного пробоя (см. рис. 3, VTl, VT2).

При повороте обозначения транзистора на схеме положение этого знака должно оставаться неизменным.

Так, чтобы изобразить лавинный транзистор, между символами эмиттера и коллектора помещают знак эффекта лавинного пробоя (см. рис. 3, VTl, VT2).

При повороте обозначения транзистора на схеме положение этого знака должно оставаться неизменным.

Рис.3. Условное обозначение лавинных транзисторов

Иначе построено обозначение однопереходного транзистора: у него один p-n-переход, но два вывода базы. Символ эмиттера в обозначении этого транзистора проводят к середине символа базы (рис. 3, VT3, VT4). Об электропроводности последней судят по символу эмиттера (направлению стрелки).

На символ однопереходного транзистора похоже обозначение большой группы транзисторов с p-n-переходом, получивших название полевых.

Основа такого транзистора — созданный в полупроводнике и снабженный двумя выводами (исток и сток) канал с электропроводностью n или p-типа.

Сопротивлением канала управляет третий электрод — затвор. Канал изображают так же, как и базу биполярного транзистора, но помещает в середине

кружка-корпуса (рис. 4, VT1), символы истока и стока присоединяют к нему с одной стороны, затвора — с другой стороны на продолжении линии истока.

Электропроводность канала указывают стрелкой на символе затвора (на рис. 4 условное графическое обозначение VT1 символизирует транзистор с каналом n-типа, VT2 – с каналом p-типа).

Канал изображают так же, как и базу биполярного транзистора, но помещает в середине

кружка-корпуса (рис. 4, VT1), символы истока и стока присоединяют к нему с одной стороны, затвора — с другой стороны на продолжении линии истока.

Электропроводность канала указывают стрелкой на символе затвора (на рис. 4 условное графическое обозначение VT1 символизирует транзистор с каналом n-типа, VT2 – с каналом p-типа).

Рис.4. Условное обозначение полевых транзисторов

В условном графическом обозначении полевых транзисторов с изолированным затвором (его изображают черточкой, параллельной символу канала с выводом на продолжении линии истока)

электропроводность канала показывают стрелкой, помещенной между символами истока и стока. Если стрелка направлена к каналу, то это значит, что изображен транзистор с

каналом n-типа, а если в противоположную сторону (см. рис. 4, VT3) — с каналом р-типа. Аналогично поступают при наличии вывода от подложки (VT4), а также при

изображении полевого транзистора с так называемым индуцированным каналом, символ которого – три коротких штриха (см. рис. 4, VT5, VT6). Если подложка соединена с

одним из электродов (обычно с истоком), это показывают внутри обозначения без точки (VT7, VT8).

рис. 4, VT5, VT6). Если подложка соединена с

одним из электродов (обычно с истоком), это показывают внутри обозначения без точки (VT7, VT8).

В полевом транзисторе может быть несколько затворов. Изображают их более короткими черточками, причем линию-вывод первого затвора обязательно помещают на продолжении линии истока (VT9).

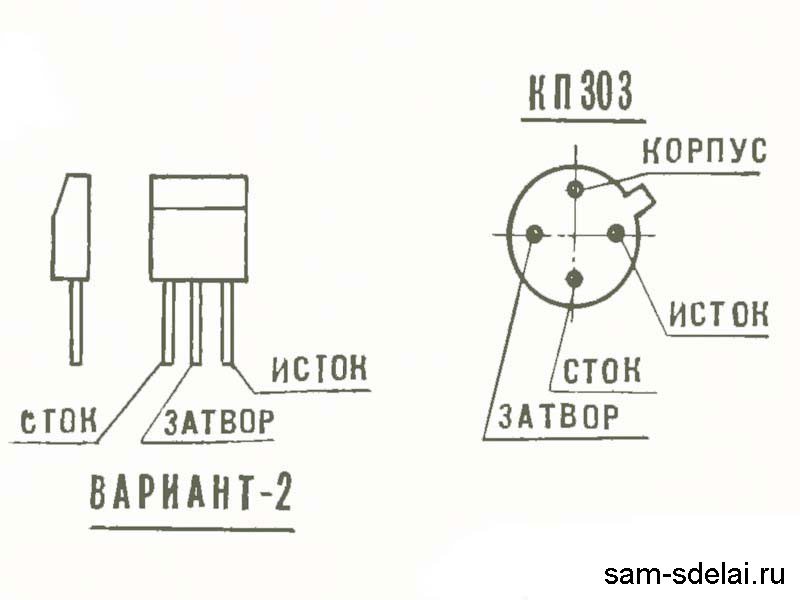

Линии-выводы полевого транзистора допускается изгибать лишь на некотором расстоянии от символа корпуса (см. рис. 4, VT1). В некоторых типах полевых транзисторов корпус может быть соединен с одним из электродов или иметь самостоятельный вывод (например, транзисторы типа КП303).

Из транзисторов, управляемых внешними факторами, широкое применение находят фототранзисторы. В качестве примера на рис. 5 показаны

условные графические обозначения фототранзисторов с выводом базы (VT1, VT2) и без него (VT3). Наряду с другими полупроводниковыми приборами, действие

которых основано на фотоэлектрическом эффекте, фототранзисторы могут входить в состав оптронов. Обозначение фототранзистора в этом случае вместе с обозначением излучателя

(обычно светодиода) заключают в объединяющий их символ корпуса, а знак фотоэффекта — две наклонные стрелки заменяют стрелками, перпендикулярными символу базы.

Обозначение фототранзистора в этом случае вместе с обозначением излучателя

(обычно светодиода) заключают в объединяющий их символ корпуса, а знак фотоэффекта — две наклонные стрелки заменяют стрелками, перпендикулярными символу базы.

Рис.5. Условное обозначение фототранзисторов и оптронов

Для примера на рис. 5 изображена одна из оптопар сдвоенного оптрона (об этом говорит позиционное обозначение U1.1). Аналогично строится обозначение оптрона с составным транзистором (U2).

Справочник “Цифровые Интегральные Микросхемы”

Справочник “Цифровые Интегральные Микросхемы” [ Содержание ] Увлекаетесь электроникой?

Приглашаем Вас принять участие

в бета-тестировании онлайн-редактора

электрических схем.

sapr.asvcorp.ru

Работайте со схемами прямо из браузера.

2.1. Основы схемотехники элементов ТТЛ

Основную логическую операцию в элементе ТТЛ выполняет

многоэмиттерный транзистор (рис. 2.1). Для удобства

рассмотрения переключения логического элемента ко входу

подключим управляющий переключатель S1, движок которого

может занимать два положения – В и Н, а к выходу подключим

резистор Rн. В положении В на вход поступит напряжение

высокого уровня, т. е. питающее напряжение Uи.п., а в

положении Н – напряжение низкого уровня, соответствующее нулю

(вход заземляем). Если на вход (рис. 2.1,0) подано

низкое напряжение (переключатель S1 поставлен в положение Н),

то появится входной ток низкого уровня

,

который будет протекать от источника питания Uип = 5 В через резистор RБ, переход база-эмиттер многоэмиттерного транзистора VT1,

контакт Н переключателя S1 на корпус. Величина этого

тока определяется сопротивлением резистора RБ:

2.1). Для удобства

рассмотрения переключения логического элемента ко входу

подключим управляющий переключатель S1, движок которого

может занимать два положения – В и Н, а к выходу подключим

резистор Rн. В положении В на вход поступит напряжение

высокого уровня, т. е. питающее напряжение Uи.п., а в

положении Н – напряжение низкого уровня, соответствующее нулю

(вход заземляем). Если на вход (рис. 2.1,0) подано

низкое напряжение (переключатель S1 поставлен в положение Н),

то появится входной ток низкого уровня

,

который будет протекать от источника питания Uип = 5 В через резистор RБ, переход база-эмиттер многоэмиттерного транзистора VT1,

контакт Н переключателя S1 на корпус. Величина этого

тока определяется сопротивлением резистора RБ:

В быстродействующих и экономичных ИС ТТЛ сопротивления резисторов RБ отличаются примерно на порядок.

Переход база – коллектор транзистора VT1 открыться не может,

так как на нем нет избыточного напряжения более чем 0,7 В = UБЭ. Напряжение на выходе

близко к нулю Uвых=О. Таким образом, переход база – эмиттер

транзистора VT1 открыт, а переход база – коллектор VT1 закрыт, т. е. многоэмиттерный транзистор VT1 находится в

активном режиме, напряжение на выходе равно нулю Uвых=О.

Если число входов транзистора VT1 более одного

(рис. 2,1,б (два из них не присоединены), то величина тока не изменится. Если все три эмиттера VT1 соединить вместе, ток практически не изменится.

Следовательно, неиспользуемые входы можно оставлять разомкнутыми.

Если заземлен хотя бы один из входов транзистора VT1 (рис. 2.1,б),

смена логических уровней на остальных входах не влияет на выходное

напряжение Uвых.

Напряжение на выходе

близко к нулю Uвых=О. Таким образом, переход база – эмиттер

транзистора VT1 открыт, а переход база – коллектор VT1 закрыт, т. е. многоэмиттерный транзистор VT1 находится в

активном режиме, напряжение на выходе равно нулю Uвых=О.

Если число входов транзистора VT1 более одного

(рис. 2,1,б (два из них не присоединены), то величина тока не изменится. Если все три эмиттера VT1 соединить вместе, ток практически не изменится.

Следовательно, неиспользуемые входы можно оставлять разомкнутыми.

Если заземлен хотя бы один из входов транзистора VT1 (рис. 2.1,б),

смена логических уровней на остальных входах не влияет на выходное

напряжение Uвых.

Переведем движок переключателя S1 в положение В (рис. 2.1,в)

(подано на вход напряжение высокого уровня), тогда переход база – эмиттер

транзистора VT1 будет закрыт, так как напряжение между базой

и эмиттером меньше или равно нулю UБЭ=<0.

Оба электрода (база и эмиттер) подключены к источнику питания Uи. п=5 В. Большой ток базы IБ течет от источника питания Uи.п. через резистор RБ, открытый переход база – коллектор,

а затем через резистор нагрузки Rн к нулевому

потенциалу (рис. 2.1,в). На коллекторе VT1 появляется

напряжение высокого уровня:

п=5 В. Большой ток базы IБ течет от источника питания Uи.п. через резистор RБ, открытый переход база – коллектор,

а затем через резистор нагрузки Rн к нулевому

потенциалу (рис. 2.1,в). На коллекторе VT1 появляется

напряжение высокого уровня:

На вход 1 поступает лишь входной ток утечки высокого уровня , не превышающий при нормальной температуре нескольких наноампер (направление тока показано на рис. 2.1,в)

Рис. 2.1. Простейшие логические элементы ТТЛ:

а – путь входного тока Iвх0; б – токи в танзисторе VT1 при низком входном уровне;

в – токи в транзисторе VT1 при высоком входном уровне;

г – токи в простейшем инверторе при высоком входном уровне

Таким образом, переход база – эмиттер транзистора VT1 закрыт, а переход

база – коллектор VT1 открыт, т. е. многоэмиттерный транзистор VT1 находится в инверсном активном режиме, напряжение на выходе

больше нуля: Uвых>0 (имеет высокий уровень).

Следовательно, на рис. 2.1,в приведен одновходовый элемент ТТЛ, реализующий логическую операцию И и не изменяющий фазу входного сигнала. Такой элемент назовем неинвертирующнм. В такой схеме активным включающим является напряжение низкого уровня и через переключатель S1 на корпус стекает большой входной ток (для стандартных элементов ТТЛ, серия К155, ток одного входа ~=1,6 мА) [1. 4].

Для получения инвертирующего логического элемента, реализующего логическую операцию И-НЕ, необходимо к многоэмиттерному транзистору VT1 добавить инвертор, выполненный на транзисторе VT2 (рис. 2.1.г).

Если на вход 1 логического элемента поступает напряжение высокого

уровня (переключатель S1 в положении В), то

многоэмиттсрный транзистор VT1 находится в

инверсном активном режиме, а транзистор VT2 насыщается базовым током IБ и выходное

напряжение, снимаемое с коллектора VТ2, будет

иметь низкий уровень, что соответствует логическому нулю (не превышает 0,3 В). Это напряжение

является напряжением насыщения коллектор – эмиттер Uкэ.нас для кремниевого транзистора VT2.

Это напряжение

является напряжением насыщения коллектор – эмиттер Uкэ.нас для кремниевого транзистора VT2.

Если на вход 1 логического элемента подать напряжение низкого уровня (переключатель S1 в положении Н), то транзистор VT2 практически закрыт, а во входной цепи течет большой ток . Выходное напряжение, снимаемое с коллектора VT2, близко к напряжению источника питания Uи.п., т. е. имеет высокий уровень, что соответствует логической единице .

Рассмотренный инвертор, выполненный на транзисторе VT2, является простым инвертором. Он используется лишь в микросхемах, выходы у которых имеют открытые коллекторы. Недостатком простого инвертора является низкая нагрузочная способность в закрытом состоянии (выходное сопротивление определяется сопротивлением резистора, стоящего в коллекторной цепи транзистора VT2).

Для повышения нагрузочной способности логического элемента вместо

простого инвертора большинство элементов ТТЛ имеют сложный инвертор

(рис. 2.2,а). Он состоит из фазоразделительного каскада, выполненного

на транзисторе VT2, и двухтактного выходного каскада,

состоящего из выходных транзисторов: насыщаемого VT5 и составного эмиттерного повторителя VT3 и VT4.

2.2,а). Он состоит из фазоразделительного каскада, выполненного

на транзисторе VT2, и двухтактного выходного каскада,

состоящего из выходных транзисторов: насыщаемого VT5 и составного эмиттерного повторителя VT3 и VT4.

Рис. 2.2.а. схема элемента со сложным инвертором

Рассмотрим функционирование логического элемента со сложным инвертором.

Подадим на вход напряжение низкого уровня, соответствующее логическому нулю

(переключатель S1 поставлен в положение Н), тогда

многоэмиттерный транзистор VT1 будет находиться в

активном режиме (переход база – эмиттер открыт, а переход

база – коллектор закрыт), течет большой ток , во входную цепь, а транзисторы VT2, VT5 закрыты (на рис. 2.2.б не показаны VT2, VT5), транзисторы VT3 и VT4 будут открыты, т. к.

база VT3 через резистор R2 подключена

к шине питания Uи. п.=5 В. Поэтому выходное напряжение,

снимаемое с нагрузки, расположенной в эмиттерной цепи VT4, будет иметь высокий уровень, что соответствует

логической единице Uвых1.

п.=5 В. Поэтому выходное напряжение,

снимаемое с нагрузки, расположенной в эмиттерной цепи VT4, будет иметь высокий уровень, что соответствует

логической единице Uвых1.

Рис. 2.2.б. распределение токов и напряжений при низком входном уровне

Статическое выходное напряжение высокого уровня для логического элемента равно: =Uи.п.-Iвых·R4-Uкэ-2·Uб.э.

Так как на транзисторах VT3, VT4 выполнен эмиттерный повторитель, то он не может перейти в состояние насыщения, и напряжение Uкэ VT4 не уменьшается меньше (0.7 .. 1) В, а напряжение Uбэ примерно равно 0,7 В для транзисторов без переходов Шотки. Падением напряжения на резисторе R4, ограничивающем ток в выходном каскаде, когда VT4 и VT5 открыты, можно пренебречь. Тогда получаем >=2,6 В.

Для транзисторов с переходами Шотки напряжение Uбэ составляет (0. 2 … 0.3) В. Следовательно, для перспективных элементов

ТТЛ напряжение высокого уровня ~= 3,5 В.

2 … 0.3) В. Следовательно, для перспективных элементов

ТТЛ напряжение высокого уровня ~= 3,5 В.

Рис. 2.2.в. распределение токов и напряжений при высоком входном уровне

Подадим на вход 1 напряжение высокого уровня (переключатель S1 поставлен в положение В) (рис. 2.2,в),

соответствующего логической единице, тогда многоэмиттерный транзистор VT1 будет находиться в инверсном активном режиме

(переход база – эмиттер закрыт, а переход база – коллектор

открыт), течет большой ток IБ в базу транзистора VT2, который откроется.

Часть эмиттерного тока транзистора VT2 поступает

в базу транзистора VT5, этот транзистор открывается и входит

в режим насыщения. Транзисторы VT3, VT4 будут закрыты.

Выходной сигнал, снимаемый с открытого и насыщенного транзистора VT5 (rкэ~=30…50 Ом), имеет

низкий уровень Uвых0~=0. 3 В, что соответствует

логическому нулю.

3 В, что соответствует

логическому нулю.

Диод VD1 предназначен для защиты входа транзистора VTl от пробоя и называется демпфирующим.

Логические элементы и их электронные аналоги (стр. 3 из 4)

Рис. 8. Логический элемент НЕ, выполненный на МОП-транзисторах с n-каналом (а), комплиментарной паре МОП-транзисторов с n- и р-каналами (б).

Логический элемент И – НЕ.

Более универсален элемент И-НЕ, позволяющий одновременно с операцией логического умножения выполнить и отрицание, тем более что в большинстве случаев это не усложняет схемы. Например, на рис. 9, а приведен МОП-вариант схемы логического элемента И-НЕ. Транзистор VT1 используется вместо сопротивления нагрузки и постоянно открыт, ибо на его затвор подается напряжение в отпирающей полярности. Если на затворы транзисторов VT2 и VT3 поданы напряжения логического 0, то они заперты, тока не проводят и на выходе Q действует почти полное напряжение питания, т. е. напряжение логической 1. Если подается напряжение логической 1 только на один из входов А или В, то состояние схемы не изменяется и напряжение на выходе остается неизменным. Однако, если на оба входа действуют напряжения логических 1, то оба транзистора VT2 и VT3 отпираются, их внутреннее сопротивление уменьшается (до 500 – 1000 Ом) и напряжение на выходе Q также становится весьма малым, т. е. на выходе действует логический 0 – в полном соответствии с таблицей истинности И-НЕ (табл. 4.).

е. напряжение логической 1. Если подается напряжение логической 1 только на один из входов А или В, то состояние схемы не изменяется и напряжение на выходе остается неизменным. Однако, если на оба входа действуют напряжения логических 1, то оба транзистора VT2 и VT3 отпираются, их внутреннее сопротивление уменьшается (до 500 – 1000 Ом) и напряжение на выходе Q также становится весьма малым, т. е. на выходе действует логический 0 – в полном соответствии с таблицей истинности И-НЕ (табл. 4.).

Радиомикрофоны на двух биполярных транзисторах . Шпионские штучки [Секреты тайной радиосвязи]

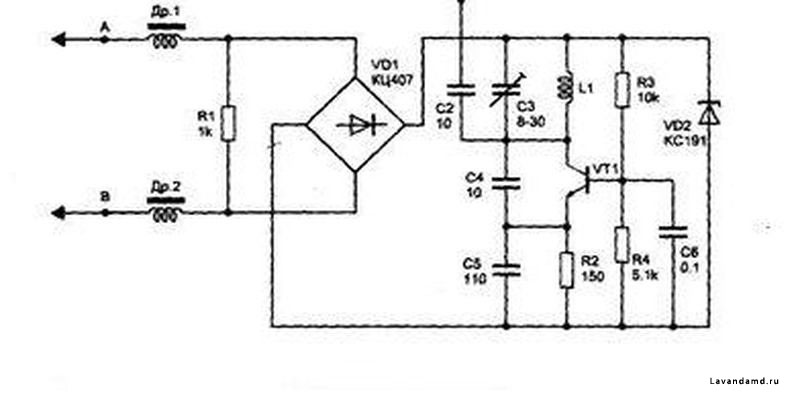

Принципиальная схема простого радиомикрофона, выполненного на двух биполярных транзисторах, приведена на рис. 5.6. В рассматриваемой конструкции, представляющей собой двухкаскадное радиопередающее устройство, на транзисторе VT1 выполнен микрофонный усилитель, а на транзисторе VT2 – генератор высокочастотных колебаний.

Рис. 5.6. Принципиальная схема простого радиомикрофона на двух биполярных транзисторах (вариант 1)

Низкочастотный сигнал, сформированный на выходе электретного микрофона BM1, через разделительный конденсатор С1 поступает на вход однокаскадного микрофонного усилителя, выполненного на транзисторе VT1. Особенностью данного усилительного каскада является использование делителя напряжения, образованного резисторами R2 и R3, для формирования напряжения смещения, подаваемого на базу транзистора VT1, включенного по схеме с общим эмиттером. С коллекторной нагрузки транзистора, образованной резистором R4, усиленный НЧ-сигнал через разделительный конденсатор С2 проходит на базу транзистора VT2, на котором выполнен генератор высокочастотных колебаний.

Особенностью данного усилительного каскада является использование делителя напряжения, образованного резисторами R2 и R3, для формирования напряжения смещения, подаваемого на базу транзистора VT1, включенного по схеме с общим эмиттером. С коллекторной нагрузки транзистора, образованной резистором R4, усиленный НЧ-сигнал через разделительный конденсатор С2 проходит на базу транзистора VT2, на котором выполнен генератор высокочастотных колебаний.

Транзистор VТ2 по постоянному току включен по схеме с общим эмиттером, а по переменному току – по схеме с общей базой, которая по высокой частоте подключена к шине корпуса через конденсатор С3. Положение рабочей точки транзистора VТ2 определяется величиной сопротивления резистора R5. Резонансный контур образован конденсатором С4 и катушкой L1 и включен в цепь коллектора транзистора. Значение рабочей частоты генератора находится в диапазоне от 100 МГц до 108 МГц и зависит от параметров катушки индуктивности L1 и величины емкости конденсатора С4. Цепь положительной обратной связи образована конденсатором С5, который включен между коллектором и эмиттером транзистора VТ2. Модулированный сигнал снимается с точки подключения конденсатора С5 цепи ОС к эмиттеру транзистора. Антенна WА1 подключается к эмиттеру транзистора VT2, поэтому ее комплексное сопротивление оказывает минимальное влияние на частоту ВЧ-генератора. В качестве антенны можно использовать отрезок медного провода диаметром 1 мм или же телескопическую антенну длиной 30 см.

Цепь положительной обратной связи образована конденсатором С5, который включен между коллектором и эмиттером транзистора VТ2. Модулированный сигнал снимается с точки подключения конденсатора С5 цепи ОС к эмиттеру транзистора. Антенна WА1 подключается к эмиттеру транзистора VT2, поэтому ее комплексное сопротивление оказывает минимальное влияние на частоту ВЧ-генератора. В качестве антенны можно использовать отрезок медного провода диаметром 1 мм или же телескопическую антенну длиной 30 см.

Питание рассматриваемого радиопередатчика осуществляется от источника постоянного напряжения 3 В, например, от двух включенных последовательно пальчиковых батареек типа АА или ААА. В качестве элемента питания можно использовать и аккумуляторы. Напряжение питания на электретный микрофон BМ1 подается через резистор R1.

К деталям, используемым при изготовлении данной конструкции, не предъявляются какие-либо особые требования. Все зависит от габаритов конструкции, которые определяют и размеры применяемых элементов. Транзистор типа KC239F можно заменить, например, импортным транзистором типа ВС239В или транзистором типа КТ3102Д отечественного производства. Высокочастотный транзистор типа KF124 можно заменить транзистором типа BF240. Номиналы резисторов R1 и R4 могут быть уменьшены до 6,8 кОм.

Транзистор типа KC239F можно заменить, например, импортным транзистором типа ВС239В или транзистором типа КТ3102Д отечественного производства. Высокочастотный транзистор типа KF124 можно заменить транзистором типа BF240. Номиналы резисторов R1 и R4 могут быть уменьшены до 6,8 кОм.

Катушка L2 наматывается на каркасе без сердечника диаметром 4,5 мм и содержит 5 витков медного посеребренного или просто луженого провода диаметром 0,7 мм.

Прием сигнала, формируемого рассмотренным радиопередатчиком, осуществляется на любой стационарный или переносной радиоприемник, который может принимать частотно-модулированные сигналы на частотах в диапазоне от 100 МГц до 108 МГц. Для данной цели рекомендуется использовать обычный вещательный радиоприемник с FM-диапазоном. Дальность действия радиопередатчика составляет примерно 25 м.

При налаживании рассмотренной конструкции могут возникнуть некоторые трудности. Например, правильный выбор рабочей точки транзистора VТ1 микрофонного усилителя требует установки напряжения на базе этого транзистора в довольно узких границах от 2,9 В до 3,2 В. При меньшем напряжении транзистор VT1 полностью закрывается, а при большем – полностью открывается.

При меньшем напряжении транзистор VT1 полностью закрывается, а при большем – полностью открывается.

Проблемы могут возникнуть и при настройке высокочастотного генератора, выполненного на транзисторе VT2. В некоторых случаях, несмотря на то, что генератор работает вполне устойчиво, качество модуляции оставляет желать лучшего. Дело в том, что у ВЧ-генераторов, выполненных по такой схеме, при определенном положении рабочей точки транзистора частота генератора практически не зависит от малых изменений коллекторного тока, инициированных модулирующим напряжением, поступающим на базу транзистора. Иными словами, положение рабочей точки транзистора, при котором обеспечивается оптимальный с точки зрения стабильности частоты режим его работы, является самым неблагоприятным с точки зрения обеспечения качественной модуляции сигнала. Поэтому при налаживании радиомикрофонов с ВЧ-генератором данного типа режим работы следует особое внимание уделить правильному выбору положения рабочей точки транзистора. Необходимо отметить, что для каждого типа транзистора указанное неблагоприятное положение рабочей точки будет иным.

Необходимо отметить, что для каждого типа транзистора указанное неблагоприятное положение рабочей точки будет иным.

Для того чтобы упростить процесс настройки предлагаемой конструкции, в ее схему рекомендуется внести незначительные изменения. Принципиальная схема усовершенствованного варианта простого радиомикрофона на двух биполярных транзисторах приведена на рис. 5.7.

Рис. 5.7. Принципиальная схема усовершенствованного варианта простого радиомикрофона на двух биполярных транзисторах

Одна из особенностей усовершенствованной схемы заключается в том, что для формирования напряжения смещения транзистора VT1 и стабилизации положения его рабочей точки используется цепь отрицательной обратной связи по напряжению. Эта цепь ОС образована резистором R2, который включен между коллектором и базой транзистора VT1. Принцип действия цепи ООС по напряжению был рассмотрен в соответствующем разделе одной из предыдущих глав.

Второе усовершенствование заключается в использовании подстроечного потенциометра R4, с помощью которого обеспечивается возможность выбора положения рабочей точки транзистора VT2 активного элемента ВЧ-генератора. В процессе налаживания радиомикрофона перемещением движка этого потенциометра следует добиться наиболее качественной модуляции высокочастотного сигнала.

В процессе налаживания радиомикрофона перемещением движка этого потенциометра следует добиться наиболее качественной модуляции высокочастотного сигнала.

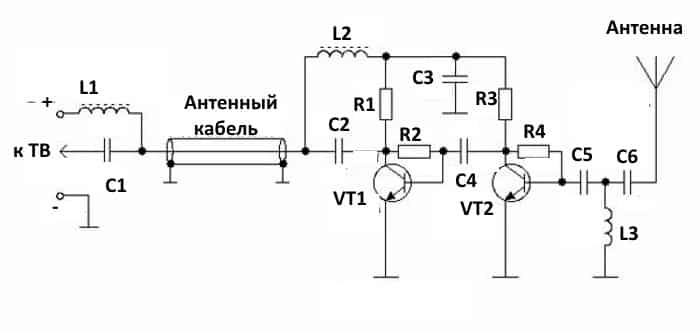

Принципиальная схема еще одного варианта простого радиомикрофона, выполненного на двух биполярных транзисторах n-p-n-проводимости, приведена на рис. 5.8.

Рис. 5.8. Принципиальная схема радиомикрофона на двух биполярных транзисторах (вариант 2)

Входной акустический сигнал преобразуется электретным микрофоном BM1, с выхода которого НЧ-сигнал через разделительный конденсатор С1 подается на базу транзистора VT1, на котором выполнен микрофонный усилитель. Для получения максимальной амплитуды неискаженного усиленного сигнала на выходе микрофонного усилителя необходимо, чтобы напряжение на коллекторе транзистора VT1 составляло примерно половину от величины напряжения питания каскада. Для стабилизации положения рабочей точки транзистора VT1 в данном случае используется схемотехническое решение, предусматривающее применение цепи отрицательной обратной связи по напряжению. Резистор R3, образующий цепь ООС, подключен между коллектором и базой транзистора VT1. Принцип действия такой схемы стабилизации был подробно рассмотрен в соответствующем разделе одной из предыдущих глав.

Резистор R3, образующий цепь ООС, подключен между коллектором и базой транзистора VT1. Принцип действия такой схемы стабилизации был подробно рассмотрен в соответствующем разделе одной из предыдущих глав.

Усиленный низкочастотный сигнал снимается с коллекторной нагрузки транзистора VT1 (резистор R4) и через конденсатор С4 и резистор R6 подается на базу транзистора VT2. Величина сопротивления резистора R6 выбирается в зависимости от характеристик примененного микрофона, поскольку со временем чувствительность электретных микрофонов ухудшается.

На транзисторе VT2 выполнен ВЧ-генератор, представляющий собой один из вариантов LC-генератора с емкостной связью. Транзистор VТ2 по постоянному току включен по схеме с общим эмиттером. Положение рабочей точки транзистора определяется величинами и соотношением сопротивлений резисторов R7 и R8. В состав мостовой схемы стабилизации положения рабочей точки также входит резистор R9. По переменному току транзистор VТ2 включен по схеме с общей базой, так как база транзистора заземлена по высокой частоте через конденсаторы С5 и С6. Резонансный контур, образованный конденсаторами С7, С8 и катушкой L1, включен в цепь коллектора транзистора VТ2. Цепь положительной обратной связи образована конденсатором С9, который включен между коллектором и эмиттером транзистора VТ2. При указанных на схеме номиналах элементов на выходе LC-генератора формируются высокочастотные колебания с частотой около 100 МГц. Таким образом, для приема сигналов данного радиопередатчика можно использовать любой вещательный радиоприемник, имеющий FM-диапазон.

Резонансный контур, образованный конденсаторами С7, С8 и катушкой L1, включен в цепь коллектора транзистора VТ2. Цепь положительной обратной связи образована конденсатором С9, который включен между коллектором и эмиттером транзистора VТ2. При указанных на схеме номиналах элементов на выходе LC-генератора формируются высокочастотные колебания с частотой около 100 МГц. Таким образом, для приема сигналов данного радиопередатчика можно использовать любой вещательный радиоприемник, имеющий FM-диапазон.

Модулирующий низкочастотный сигнал поступает с выхода микрофонного усилителя на базу транзистора VT2, что приводит к изменению положения его рабочей точки по закону модулирующего сигнала. В результате аналогичным образом изменяется рабочая частота ВЧ-генератора, то есть на его выходе формируется частотно-модулированный сигнал. Этот сигнал через катушку связи L2 подается на антенну.

Питание данного радиопередающего устройства осуществляется от двух включенных последовательно батареек типа ААА или от аккумуляторов напряжением 3 В, например, типа CR2032 (Ш20ґ3,2 мм) или типа CR2330 (Ш23ґ3,0 мм). Потребляемый ток не превышает 5 мА. Напряжение питания электретного микрофона формируется цепочкой, образованной резисторами R1, R2 и конденсатором С2. Параллельно источнику питания подключены конденсаторы С11 и С12, обеспечивающие шунтирование источника по высокой частоте.

Потребляемый ток не превышает 5 мА. Напряжение питания электретного микрофона формируется цепочкой, образованной резисторами R1, R2 и конденсатором С2. Параллельно источнику питания подключены конденсаторы С11 и С12, обеспечивающие шунтирование источника по высокой частоте.

Катушка L1 наматывается на каркасе без сердечника диаметром 5 мм и содержит 7 витков медного посеребренного провода диаметром 1 мм. Непосредственно на катушку L1 наматывается катушка L2, содержащая 3 витка изолированного провода. К нижнему по схеме выводу катушки L2 подключается антенна, представляющая собой отрезок провода длиной около 60 см.

Транзистор типа KC239C можно заменить, например, импортным транзистором типа ВС239В или транзистором типа КТ3102Д отечественного производства. Высокочастотный транзистор типа KF525 выполнен в металлическом корпусе с выводом, который необходимо припаять к шине корпуса. Вместо транзистора типа KF525 можно использовать транзисторы типа KF524, BF199, BF224, SF240, SF245, KSY71 или KSY72.

При налаживании грубая настройка обеспечивается изменением расстояния между витками катушки L1. Уменьшение расстояния между витками этой катушки приводит к уменьшению значения рабочей частоты генератора, а с увеличением расстояния между витками рабочая частота ВЧ-генератора увеличивается. Точная настройка значения частоты ВЧ-генератора осуществляется с помощью конденсатора С7.

При необходимости в каркасе катушки L1 можно установить сердечник. В этом случае точное значение рабочей частоты ВЧ-генератора выбирается за счет изменения положения этого сердечника по отношению к виткам катушки L1. Использование сердечника из ферромагнитного материала приводит к уменьшению значения рабочей частоты. Если же применить сердечник из меди или алюминия, то рабочая частота увеличится. В процессе налаживания не следует забывать о том, что при перемещении сердечника катушки L1 изменяется степень связи между этой катушкой и катушкой L2.

|

Навигация: Главная Случайная страница Обратная связь ТОП Интересно знать Избранные Топ: Теоретическая значимость работы: Описание теоретической значимости (ценности) результатов исследования должно присутствовать во введении. Организация стока поверхностных вод: Наибольшее количество влаги на земном шаре испаряется с поверхности морей и океанов… Марксистская теория происхождения государства: По мнению Маркса и Энгельса, в основе развития общества, происходящих в нем изменений лежит… Интересное: Национальное богатство страны и его составляющие: для оценки элементов национального богатства используются… Подходы к решению темы фильма: Существует три основных типа исторического фильма, имеющих между собой много общего… Аура как энергетическое поле: многослойную ауру человека можно представить себе подобным… Дисциплины: Автоматизация Антропология Археология Архитектура Аудит Биология Бухгалтерия Военная наука Генетика География Геология Демография Журналистика Зоология Иностранные языки Информатика Искусство История Кинематография Компьютеризация Кораблестроение Кулинария Культура Лексикология Лингвистика Литература Логика Маркетинг Математика Машиностроение Медицина Менеджмент Металлургия Метрология Механика Музыкология Науковедение Образование Охрана Труда Педагогика Политология Правоотношение Предпринимательство Приборостроение Программирование Производство Промышленность Психология Радиосвязь Религия Риторика Социология Спорт Стандартизация Статистика Строительство Теология Технологии Торговля Транспорт Фармакология Физика Физиология Философия Финансы Химия Хозяйство Черчение Экология Экономика Электроника Энергетика Юриспруденция |

⇐ ПредыдущаяСтр 31 из 40Следующая ⇒

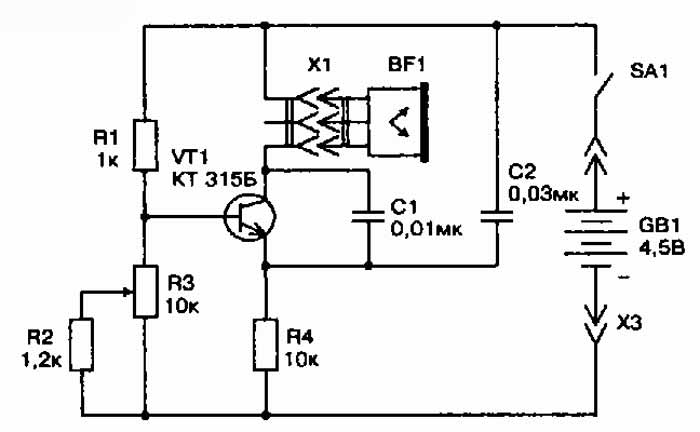

Транзисторная схема триггера Шмитта. Рис. 13.11

В результате потенциалы базы и эмиттера транзистора VT2 будут равны. Транзистор VT2 закроется. На выходе установится напряжение, равное напряжению питания. При уменьшении входного напряжения транзистор VT1 выходит из режима насыщения. Наступает лавинообразный процесс. Эмиттерный ток транзистора VT2, создающий закрывающее напряжение на резисторе R3, ускоряет закрывание транзистора VT1. В результате триггер возвращается в исходное состояние. Рис. 13.12

Триггер Шмитта на ОУ. Здесь (рис. 13.12, а) в качестве порогового элемента используется ОУ с ПОС. Связь зависит от сопротивлений резисторов. Для простоты расчета основных характеристик схемы можно принять R1 равным 10 Ом. После того как будут рассчитаны резисторы R2 и R3, можно все номиналы пропорционально умножить на коэффициент, который обеспечит подходящие сопротивления резисторов. Резисторы R2 и R3 рассчитываются по формулам Однако сопротивления резисторов не должны превышать 1/10 входного сопротивления ОУ. Эпюры входного и выходного напряжений приведены на рис. 13.12, б. Рис. 13.13

Гистерезисная пороговая схема на ОУ. Для выбора параметров схемы (рис. 13.13) следует предположить, что входное сопротивление усилителя значительно больше сопротивлений применяемых резисторов, а выходное сопротивление значительно меньше сопротивления нагрузки. Нулевое напряжение смещения получается при условии R1R2/(R1+R2)=R3R4/(R3+R4). Напряжения, при которых схема переходит из одного состояния в другое, определяется из уравнений С помощью этих выражений получим R4=R3(Eol — E02)/(U1 — U2). Гистерезисные схемы на усилителе К284УД1. На рис. 13.14 приведены четыре схемы на ОУ К284УД1, которые имеют передаточные характеристики гистерезисного вида. Основные параметры характеристик можно рассчитать по следующим формулам. Для схемы рис. Uсм — напряжение смещения микросхемы; E0, Emax, Emin, Uсм берутся с учетом знака.

Рис. 13.15 Рис. 13.16

Ограничитель с управляемыми порогами срабатывания. Усилитель-ограничитель построен на трех ОУ (рис. 13.15) и создает выходной сигнал, пропорциональный входному сигналу до тех пор, пока входной сигнал находится между уровнями ограничения. Пороги ограничения устанавливаются на входе ОУ DA2 и DA3. Когда выходной сигнал превышает эти уровни, открывается один из усилителей и через диод подается сигнал ООС на вход ОУ DA1. Коэффициент усиления ОУ DA1 резко уменьшается. Происходит ограничение входного сигнала. Уровни ограничения в интегральных микросхемах могут меняться от нуля до максимально допустимого напряжения на входе ОУ. Двухполярный ограничитель на интегральной микросхеме. Односторонние ограничители.В ограничителях (рис. 13.17) цепь ООС состоит из нелинейных элементов. Для положительного входного сигнала применяется схема рис. 13.17, а, а для отрицательного сигнала — рис. 13.17, б. Когда напряжение на выходе ОУ не превышает напряжения пробоя стабилитрона, выходной сигнал линейно зависит от входного сигнала с коэффициентом передачи R2/R1. Рис. 13.17 Рис. 13.18

Двухсторонний ограничитель. Схемы (рис. 13.18) имеют два порога ограничения. Один порог ограничения определяется напряжением пробоя стабилитрона, а второй зависит от падения напряжения на открытом стабилитроне. Прямое падение напряжения стабилитрона близко к значению 0,7 В. Если в схеме (рнс. 13.18, а) управляющее напряжение имеет положительную полярность, то уровень пробоя стабилитрона уменьшается. При всех значениях управляющего напряжения на входе появляется постоянная составляющая, которая иногда может привести к нежелательным последствиям. Чтобы исключить влияние управляющего напряжения на вход, в схеме (рис. 13.18, б) применена токовая регулировка порогами ограничения. Напряжение на выходе меняется в зависимости от управляющего сигнала UВЫХ= (R2/R3)E. На инвертирующем входе напряжение остается равным нулю. Меняя полярность Е, можно устанавливать разные уровни ограничения. В ограничителе можно применить различные ОУ. Ограничитель с динамическим порогом. Операционный усилитель, являющийся основным элементом ограничителя (рис. 13.19), имеет две цепи ООС: положительная полярность входного сигнала проходит через диод VD2 и резистор R3, а отрицательная полярность — через VD1 и R2. Рис. 13.19 Рис. 13.20

«Гистерезисный» ограничитель. Для рассмотрения работы ограничителя (рис. 13.20) положим E = 0. На стабилитроне за счет ПОС устанавливается напряжение Uc. На неинвертирующем входе присутствует пороговое напряжение, равное U0= (R1/R2) Uc. Для напряжения UC>E>0 ОУ переключается при напряжении на входе U1 — E+(R1/R2)U0. В исходное состояние ОУ возвращается при входном сигнале, равном Е. Если E>UC, то ОУ работает как ограничитель входного сигнала с порогом E. При замене стабилитрона транзистором с регулируемым базовым напряжением можно получить ограничитель с меняющейся границей переключения. Ограничитель на стабилитронах. Ограничитель низкочастотных сигналов состоит из ОУ, коэффициент усиления которого определяется отношением сопротивлений резисторов R2/R1, и двумя стабилитронами, включенными навстречу друг другу (рис. Рис. 13.21 Рис. 13.22 Рис. 13.23

Преобразователь синус-меандр. Формирователь (рис. 13.22) преобразует напряжение синусоидальной формы в импульсное. Амплитуда прямоугольного выходного сигнала прямо пропорциональна амплитуде гармонического сигнала. Входной сигнал (более 0,5 В) проходит через диод VD2 и заряжает конденсатор С1. Ограничитель гармонического сигнала. Устройство (рис. 13.23) преобразует гармонический сигнал в импульсный. Отрицательная полуволна гармонического сигнала через диод VD2 заряжает конденсатор. За это время открывается транзистор. Положительная полуволна закрывает транзистор. В результате постоянное напряжение на конденсаторе преобразуется транзистором в переменное. Частота следования импульсов определяется частотой входного сигнала. Минимальный сигнал, с которого начинается преобразование, равен 200 мВ.

ПОРОГОВЫЕ УСТРОЙСТВА

Многопороговое устройство. Устройство с малой петлей гистерезиса. В схеме сравнения двух напряжений (рис. 13.25) применяется запаздывающая ОС. Эта связь позволяет уменьшить гистерезис передаточной характеристики релаксационной схемы. На входе устройства стоит дифференциальный усилитель, выходной сигнал которого подается на формирователь, построенный на транзисторах с разными типами проводимости и охваченным ПОС через цепочку R2C1. Кроме того, с коллектора транзистора VT2 подается ООС через цепочку R3, С2. Отрицательная обратная связь через время r=RiCz компенсирует действие ПОС. Рис. 13.24

Преобразователь гармонического сигнала в прямоугольный. Преобразование сигнала (рис. 13.26) осуществляется за счет насыщения транзисторов. Положительная полуволна входного сигнала шунтируется диодои VD1. Отрицательная полуволна открывает транзистор VT1. Коллекторный ток этого транзистора открывает транзистор VT2. Отрицательное напряжение 5 В проходит через диоды VD2 и VD3 и подается на выход. Рис. 13.25

Выходное сопротивление устройства для однополярного сигнала менее 500 Ом, а для двухполярного — 20 кОм; частота входного сигнала 1 кГц, амплитуда 5 В. Ограничитель-дискриминатор. Устройство (рис. 13.27) имеет регулируемый порог ограничения. Входной сигнал с амплитудой 1 В может быть разделен на две составляющие. При установке на входе 10 напряжения 1 В на выход проходит сигнал положительной полярности. Установкой на входе 10 напряжения — 1 В на выходе формируется сигнал отрицательной полярности. Рис. 13.26 Рис. 13.27 Рис. 13.28 Рис. 13.29

Разделитель сигналов. Пороговое устройство. В пороговом устройстве (рис. 13.29) используются элементы ИЛИ/ИЛИ — НЕ. Через резистор R2 в схему вводится ПОС, а резистор R1 развязывает источник сигнала от входа схемы. Сравнивающее устройство.Сравнивающее yqTpoflcTBO (рис. 13.30) вырабатывает выходной сигнал, длительность которого равна длительности превышения одного входного сигнала над другим. Дифференциальные усилители включены последовательно один за другим и работают в режиме ограничения сигнала, рассогласования. Количество включенных последовательных усилителей определяет ширину зоны нечувствительности устройства. Рис. 13.30 Рис 13.31

При изменении напряжения питания на ±10 % ширина зоны нечувствительности не более 1 мВ Дрейф порога срабатывания не более 15 мкВ/град в диапазоне температур 20 — 70°С Максимальная амплитуда входного сигнала ±2 В, диапазон рабочих частот О — 500 кГц Выходной сигнат более 4 В Компараторы на микросхемах К133ЛАЗ. Компаратор на рис 13.31, б построен на четырех логических элементах Все элементы находятся в режиме, близком к линейному Это достигнуто введением резисторов R3 — R6 Передаточная характеристика элемента 2И — НЕ в зависимости от сопротивления на его входе показана на рис 1331, г Регулировкой входного сопротивления можно управлять напряжением на выходе элемента. Рис 13.32 Входной сигнал подается в точку, где напряжение равно нулю Этот уровень устанавливается резистором R2 Время включения и выключения компаратора определяется временем переключения одного элемента Один элемент имеет время задержки включения не более 18 не, а время задержки выключения не более 36 не Чувствительность схемы составляет 1 — 2 мВ Компаратор на логических элементах. Компаратор напряжения построен на двух логических элементах микросхемы К133ЛАЗ На рис 1332, а изображена схема, в которой сравниваются два напряжения На Вход 1 подается эталонное напряжение, а на Вход 2 — исследуемое Чувствительность схемы равна 5 мВ Если сигнал в точке соединения резисторов R1 — R3 меньше 3 мВ, то на выходе существует постоян шй уровень 2 В При сигнале с напряжением 4 мВ формируется отрицатечьный импучьс (рис 1332, в), а сигнал с напряжением 5 мВ вызывает появление положительного импульса Для управления порогом срабатывания компаратора (рис 1332, б) на вход 2 элемента DD1 подается напряжение Это напряжение определяет порог срабатывания схемы как для положительных, так и лля отрицательных попярностей входного сигнала Двухполяоныи выходной сигнал формируется от гармонического входного сигнала с амплитудой 4 мВ Точная настройка схемы позволяет увеличить чувствительность до 1 мВ Однако в этом случае выходной сигнал меняется от +2 до 0 В Дифференциальная схема компаратора. Рис 13.33 Рис. 13.34

Глава 14 ПРЕОБРАЗОВАТЕЛИ ЧАСТОТЫ

Преобразователи частоты осуществляют перенос спектра исследуемого сигнала из одной части частотного диапазона в другую. Наиболее перспективными преобразователями являются балансные. Эти преобразователи при тщательной настройке осуществляют подавление на выходе сигнала гетеродина более чем на 80 дБ. Их выполняют как на биполярных, так и на полевых транзисторах. Использование в преобразователях полевых транзисторов с квадратичной характеристикой позволяет осуществить перемножение входного и гетеродинного сигналов с очень малым уровнем перекрестных искажений, зависящим в основном от паразитных межэлектродных емкостей. К преобразователям частоты следует отнести также схемы, осуществляющие умножение и деление частоты гармонического сигнала. Деление частоты гармонического сигнала можно осуществить двумя способами: с опорным сигналом и без него. В регенеративных делителях частоты входной сигнал через цепь ОС взаимодействует с гармоникой, которая образуется при нелинейном преобразовании входного сигнала. Такие делители являются широкополосными. Они позволяют получить коэффициент деления более 5, причем можно получить и дробный коэффициент деления. При значительном увеличении коэффициента деления существенно искажается форма выходного сигнала. С применением гетеродинного сигнала в делителях частоты значительно упрощаются схемы. При этом не обязательно осуществлять умножение входного и гетеродинного Сигналов. Сложение входного и гетеродинного сигналов с последующим детектированием образует сигнал с разностной частотой. Способ включения ОУ, который применяется в схеме, можно найти в гл. 1. ⇐ Предыдущая26272829303132333435Следующая ⇒ Индивидуальные и групповые автопоилки: для животных. Механическое удерживание земляных масс: Механическое удерживание земляных масс на склоне обеспечивают контрфорсными сооружениями различных конструкций… Общие условия выбора системы дренажа: Система дренажа выбирается в зависимости от характера защищаемого… Папиллярные узоры пальцев рук – маркер спортивных способностей: дерматоглифические признаки формируются на 3-5 месяце беременности, не изменяются в течение жизни… |

vt1%20транзистор техпаспорт и примечания по применению

Недоступно

Резюме: нет абстрактного текста

Текст: ток коллектора и глубина модуляции SFH601 -4 VCEsat=f (lc) (TA=25°C) Рисунок 20. Транзистор

OCR-сканирование

Недоступно

Резюме: нет абстрактного текста

Текст: ) Рис. 20. Емкость транзистора C -f(V o ) (Ta=25°C, f=1 МГц) 0 ,1 [· 0 i-i- – L I 10

OCR-сканирование

lc приборная панель 2 b-5

Резюме: нет абстрактного текста

Текст: ) Рис. 20. Емкость транзистора C=f(VQ) (Ta=25°C, f=1 МГц) ≥ SFH600 5-212

OCR-сканирование

РЛ2010-54.1К-138-Д1

Резюме: термоник YD80SM-12 PN2222A до-92 80-Вт1 ШИМ термистор термистор 100k 2N2222A MIC502 MIC502BM

Текст: Нет доступного текста файла

Оригинал

1К-138-Д1

термоника

Ярд80СМ-12

PN2222A к-92

80-вт1

ШИМ термистор

термистор 100k

2Н2222А

MIC502BM

1К-138-Д1

термоника

Ярд80СМ-12

PN2222A к-92

80-вт1

ШИМ термистор

термистор 100k

2Н2222А

MIC502BM2014 – MIC502YM

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

2003 – YD80SM-12

Резюме: 12 В – управление скоростью вращения вентилятора с помощью термистора 2003 ATX ШИМ-управление PN2222A ЭКВИВАЛЕНТ RL201054

Текст: Нет доступного текста файла

Оригинал

1998 – mic502 ic

Резюме: YD80SM-12 2N2222A MIC502 MIC502BM MIC502BN 240 термистор ntc 100k Линейный драйвер вентилятора

Текст: Нет доступного текста файла

Оригинал

2002 – транзистор vt1

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

2001 – транзистор vt1

Реферат: УПРАВЛЕНИЕ ВЕНТИЛЯТОРОМ 24В С ИСПОЛЬЗОВАНИЕМ ТЕРМИСТОРА thermonics Термистор ШИМ термистор-резистор YD80SM-12 УПРАВЛЕНИЕ ВЕНТИЛЯТОРОМ 12В С ИСПОЛЬЗОВАНИЕМ ТЕРМИСТОРА MIC502BN MIC502BM MIC502

Текст: Нет доступного текста файла

Оригинал

2001 – YD80SM-12

Аннотация: УПРАВЛЕНИЕ ВЕНТИЛЯТОРОМ 12 В С ИСПОЛЬЗОВАНИЕМ ТЕРМИСТОРА MIC502 PWM IC 8-PIN DIP vt1 транзистор MIC502BN MIC502BM 2N2222A thermonics RL201054

Текст: Нет доступного текста файла

Оригинал

1999 г. – нет в наличии

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

термистор 502 на

Резюме: IC502 24V ВЕНТИЛЯТОР УПРАВЛЕНИЕ С ИСПОЛЬЗОВАНИЕМ ТЕРМИСТОРА IC 502 термистор 502

Текст: Нет доступного текста файла

OCR-сканирование

Недоступно

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

OCR-сканирование

2010 – Недоступно

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

2003 – 112206

Резюме: mic502 ic 12V FAN CONTROL BY USING THERMISTOR datasheet драйвер бесколлекторный охлаждающий вентилятор постоянного тока mic502 MIC502BM MIC502BN MIC502YM

Текст: Нет доступного текста файла

Оригинал

IC502

Реферат: УПРАВЛЕНИЕ ВЕНТИЛЯТОРОМ 24В С ПОМОЩЬЮ ТЕРМИСТОРА K138

Текст: Нет доступного текста файла

OCR-сканирование

Недоступно

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

2003 – Недоступно

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

2011 – HMC1000LP5E

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

2002 – ВСК9182

Реферат: Транзистор vt1 GR-253-CORE VSC9187 VSC9188

Текст: Нет доступного текста файла

Оригинал

2009 – Калибровка гироскопа

Аннотация: автожир Ан-1049

Текст: Нет доступного текста файла

Оригинал

2002 – ГР-1400-ЯДЕР

Резюме: GR-253-CORE VSC9182 VSC9186 VSC9187 VSC9188 cdr 03a

Текст: Нет доступного текста файла

Оригинал

2012 – LTC2995IUD

Реферат: ИМС уд 1803 маркировка T01 SOT 1332V UV диод LTC2997

Текст: Нет доступного текста файла

Оригинал

2012 – Недоступно

Резюме: нет абстрактного текста

Текст: Нет доступного текста файла

Оригинал

ЛМ56

Реферат: lm568 HVAC ТЕРМОСТАТ СХЕМА M08A LM56CIMX LM56CIM LM56BIMX LM56BIMMX LM56BIMM термостат rc

Текст: Нет доступного текста файла

Оригинал

Предыдущий 1 2 3 … 23 24 25 Далее

Усовершенствованные компараторы для лучшего дизайна

Автор статьи: Михаил А. Шустов- Категория : Аналог

- 2022-09-16

- (0) Комментарии

Аналоговые и цифровые компараторы позволяют сравнивать входные сигналы по их уровню.

ИС традиционных цифровых компараторов являются электронными аналогами механических рычажных весов. Как и их механические аналоги, они сравнивают два логических сигнала и выдают результат (обычно уровень напряжения), указывающий соотношение входных сигналов, т. е. A > B, A < B, а в некоторых случаях A = B.

Как бы ни были полезны эти простые компараторы, у них есть несколько проблем, в том числе:

- Чтобы получить визуальную индикацию сравнения, выход компаратора должен быть подключен к транзистору, который управляет светодиодом.

- Если компаратор используется для контроля наличия двух питающих напряжений, возникает ошибка, если оба источника входного напряжения отключены. В этом случае цифровой компаратор покажет вводящее в заблуждение «нормальное» состояние, т. е. A = B, даже если оба источника питания не работают.

Компаратор, представленный в этом DI, решает эти проблемы и добавляет некоторые другие полезные функции. Он основан на дискретных элементах, что позволяет добиться максимального результата при минимуме электронных компонентов. Кроме того, это решение обеспечивает визуальную индикацию (с помощью светодиодов) ранее доступных состояний сравнения (A > B; A < B и A = B), а также индикацию состояния входов, когда A = B = 0 и A = B = 1.

Кроме того, это решение обеспечивает визуальную индикацию (с помощью светодиодов) ранее доступных состояний сравнения (A > B; A < B и A = B), а также индикацию состояния входов, когда A = B = 0 и A = B = 1.

Прежде чем мы углубимся в детали, давайте рассмотрим некоторые различия между аналоговыми и цифровыми компараторами.

Аналоговые компараторы обычно имеют настраиваемый порог переключения. Если входной сигнал превышает этот порог, выходной сигнал компаратора переключает выходной уровень с логической единицы на логический ноль или наоборот.

Цифровые компараторы позволяют сравнивать соотношение уровней логических сигналов на входах А и В. Эти устройства могут отображать: А = В; А > В; A < B.

На рисунках 2-4 показаны схемы простых универсальных компараторов, использующих несколько светодиодов (LED1–LED3) для индикации соотношений между уровнями входов A и B следующим образом:

Эквивалентную схему состояний можно увидеть на Рис. 1.

1.

Рис. 1 Основные улучшенные эквивалентные схемы компаратора.

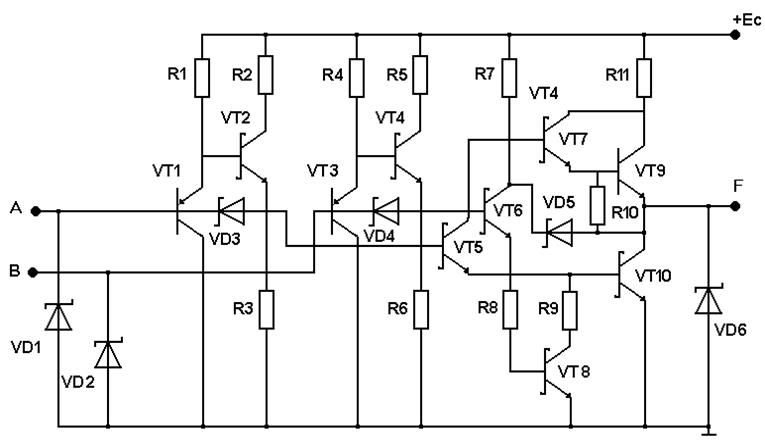

Схема 1: компаратор, реализованный с использованием биполярных транзисторов

Компаратор, показанный на рис. 2 , состоит из биполярных транзисторов VT1, VT2 и трех упомянутых ранее светодиодных индикаторов состояния.

Рисунок 2 Компаратор на биполярных транзисторах.

Схема работает следующим образом:

При отсутствии сигналов логического уровня на входах A и B транзисторы закрыты (выключены), в результате чего ток через LED3 протекает через резисторы R1, R3 и R2, R4. Этот светодиод указывает на состояние A = B = 0.

Если на вход A подается единичный сигнал логической «1», а на вход B подается логический ноль, транзистор VT1 открывается (включается), вызывая загорание LED1 , что свидетельствует о том, что А > В.

Если на вход В подается единичный сигнал логической «1», а на вход А подается логический ноль, транзистор VT2 открывается и загорается светодиод 2, указывая на состояние А < В.

Если на оба входа А и В подается единичный сигнал логической «1», то оба транзистора VT1 и VT2 будут открыты, так что ни один из светодиодов не загорится, указывая на состояние А = В = 1.

Компаратор, показанный на рис. 2, имеет порог переключения около 3 В. Эта схема имеет интересную особенность, поскольку переключение светодиодов происходит не мгновенно, а в виде постепенного изменения их яркости. Эта характеристика делает этот тип компаратора удобным для использования для мониторинга уровня стереофонических аудиосигналов. Его также можно подключить к выходам стереоусилителя и использовать для управления разноцветными светодиодами, добавляющими визуальный эффект музыкальным композициям.

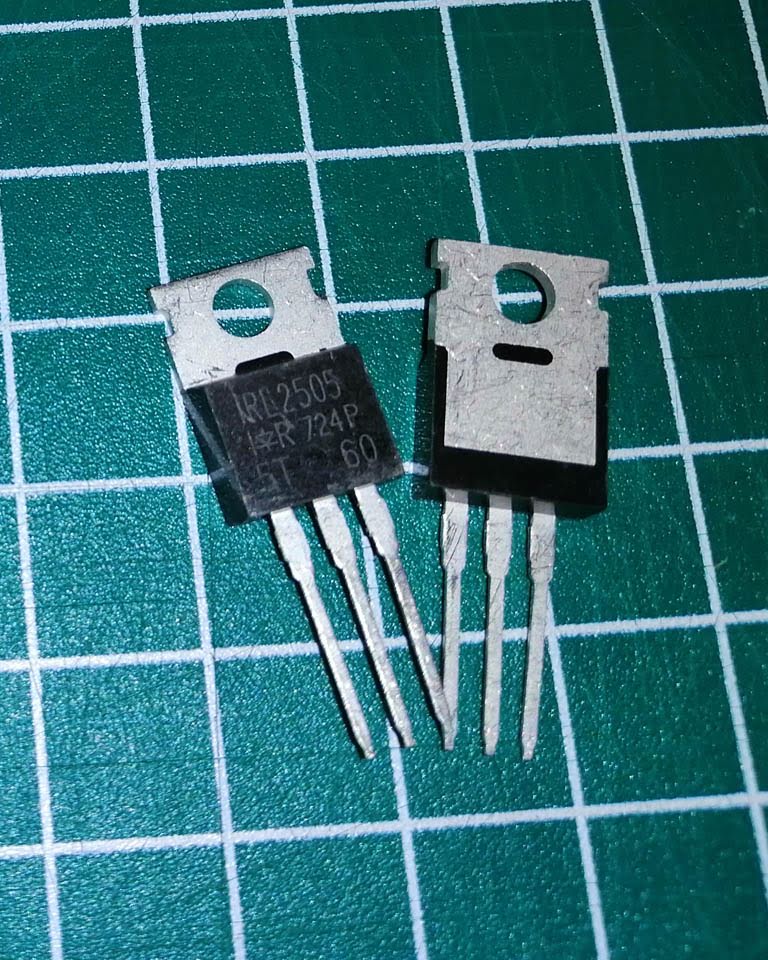

Схема 2: Усовершенствованный компаратор, реализованный на полевых транзисторах

Цифровой компаратор на полевых транзисторах, показанный на рис. 3 , также имеет порог переключения 3 В, что позволяет использовать его в ТТЛ или КМОП цифровых устройствах, работающих на логических уровнях от 3 до 15 В, а возможно и выше.

При необходимости пороги переключения компараторов на рисунках 2 и 3 можно отрегулировать, изменив значения входных резистивных делителей (например, R5 и R6, R7 и R8).

Рисунок 3 Компаратор на биполярных транзисторах.

Схема 3: усовершенствованный компаратор с регулируемым порогом

Цифровой компаратор, показанный на рис. 4 , основан на микросхеме компаратора A1 LM393 и имеет регулируемый порог, который можно плавно изменять от 0 до 20 В с помощью потенциометра R3. .

Рис. 4 Цифровое сравнение на основе микросхемы компаратора A1 LM393.

Выводы и приложения

Цифровые компараторы, показанные на рис. 2-4, могут полностью решить проблему контроля двух напряжений питания, поскольку они обеспечивают точную индикацию того, какое из напряжений отсутствует. Напряжение питания всех этих компараторов не критично и почти всегда может использовать существующий источник питания приложения; при условии, что оно составляет 5 В или выше.

Эти усовершенствованные схемы компараторов устраняют «слепую зону» в обычных конструкциях, когда невозможно различить, находятся ли оба входа в состоянии «1» или «0». Все три конструкции, описанные в этом DI, также имеют встроенную возможность управления светодиодами.

Этот тип схемы также может быть адаптирован для некоторых других интересных применений помимо контроля источников питания, включая:

- Двухканальный логический тестер, позволяющий визуально контролировать наличие и уровень логических уровней в двух точках цифрового устройства. находится под наблюдением или ремонтом.

- Схема для гальванически изолированной передачи данных при использовании оптронных пар в качестве светодиодов, в том числе с открытым оптическим каналом.

- Защитная блокировка, которая не позволит активировать механизм, пока два (или более) датчика не укажут, что он правильно сконфигурирован.

- Компаратор с переменным порогом (контур 3) можно модифицировать для использования в качестве простого аналогового аварийного сигнала для температуры, напряжения или других переменных.

Эта статья была первоначально опубликована EDN .

Виртуальные онлайн-мероприятия — EAC 2022 (18–20 октября)

Выставочный стенд:

Новые продукты и решения, загрузка технических документов, типовые проекты, видеоролики

Сессии конференции:

- Интернет вещей (IoT)

- Цепочка поставок

- Автомобильная электроника

- Волна беспроводной связи

Розыгрыш на 3 раунда:

Зарегистрируйтесь, присоединяйтесь к конференции и посетите стенды, чтобы получить шанс выиграть отличные призы.

ЗАРЕГИСТРИРУЙТЕСЬ СЕЙЧАС

- Теги :

- Design Ideas

Время попрощаться с ggNMOS Snapback для защиты от электростатического разряда – SOFICS – Решения для микросхем

RIP Зажим ggNMOS ESD – спасибо за годы самоотверженной работы и обслуживанияSnapback ggNMOS уже много лет является нашим супергеройским антистатическим устройством. Благодаря правильному анализу, пониманию и некоторым хитростям инженеры ESD по всему миру полагались на него и завоевали уважение своих коллег. Инженеры могли произвести впечатление на своих коллег, которые считали, что это чистая магия. ggNMOS был нашей опорой и источником силы.

Однако в последние годы ggNMOS было трудно следить и адаптироваться ко всем новейшим инновациям и масштабированию процессов. Мы все еще могли полагаться на него в особых случаях, но стало ясно, что конец близок.

С уходом из жизни ggNMOS оставляет за собой наследие надежных продуктов ИС.

Инженеры по ИС, разрабатывающие зажимы для защиты от электростатического разряда для чипов в зрелых низковольтных (5 В или ниже) технологиях CMOS (0,18 мкм или старше), избалованы. В этих процессах диоды ESD могут проводить большой ток ESD, типичные расчетные окна ESD очень широки, а NMOS-транзистор является идеальным фиксатором защиты от ESD для большинства комбинаций нагрузок.

Snapback Защита от электростатического разряда на основе NMOS

В этих зрелых технологических узлах NMOS-транзистор сочетает в себе несколько хороших характеристик во время событий электростатического разряда

- Операция Snapback, когда активируется паразитный биполярный NPN-транзистор .

- Небольшого устройства достаточно для стандартной устойчивости к электростатическим разрядам (It2) благодаря высокой производительности NPN .

- Эффективная защита для большинства функциональных цепей благодаря низкому напряжению срабатывания (Vt1), определяемому пробоем перехода сток-подложка, ниже типичного напряжения отказа цепей оксида затвора и сердечника.

- Низкий риск защелкивания , поскольку напряжение фиксации/удержания (Vh), определяемое бета-вариантом NPN, выше напряжения питания.

Благодаря этим характеристикам NMOS-транзистор используется в качестве фиксатора электростатического разряда в различных местах микросхемы в зрелых процессах.

- ggNMOS можно использовать как силовой зажим устройство

- Конструкторы используют это устройство также в качестве локальной защиты для защиты входных затворов

- Выходные драйверы могут быть легко изготовлены зажим

- Вторичная защита может быть использована для расширения окна проектирования ESD для более чувствительных цепей

«NMOST с заземленным затвором (ggNMOST) —

одна из рабочих лошадок в области ESD».

Постоянно обновляется и совершенствуется

Поскольку это такой хороший, универсальный подход, многие инженеры по электростатическим разрядам и инженеры-технологи по всему миру придумали трюки, чтобы максимизировать удобство использования при внесении изменений в технологический процесс. Во многих публикациях содержится подробная информация о добавлении фиктивных пальцев, масках блокировки nLDD, блокировке силицида, балластировке на заднем конце, методах срабатывания нескольких пальцев и масках имплантатов ESD.

Быстрая реакция NMOS-транзистора (с толстым оксидом) в 180-нм CMOS-процессе. К сожалению, все хорошие истории когда-нибудь заканчиваются . Основываясь на хорошем опыте работы со зрелыми узлами, инженеры задались вопросом, можно ли использовать Snapback NMOS также в более продвинутых процессах CMOS, FinFET, высокого напряжения, BCD или SOI. Литейные заводы продвигали использование NMOS-транзистора snapback для защиты от электростатического разряда в каждом из этих процессов, но это привело к большому количеству отказов продукта.

Литейные заводы продвигали использование NMOS-транзистора snapback для защиты от электростатического разряда в каждом из этих процессов, но это привело к большому количеству отказов продукта.

Передовая технология CMOS

Например, в более продвинутом техпроцессе совсем не мрачно. Существует ряд тенденций , которые играют роль в отказе от защиты от электростатического разряда на основе ggNMOS для наиболее чувствительных интерфейсов.

Масштабирующие транзисторы и следование закону Мура хорошо служили отрасли более 50 лет, создавая более плотные, дешевые, более производительные и менее потребляющие интегральные схемы. – «Тенденции масштабирования CMOS и не только», https://www.computer.org/csdl/magazine/mi/2017/06/mmi2017060020/13rRUwI5TUw- Соединения стали более мелкими, а размеры — меньшими в каждом последующем узле процесса. Этот уменьшенный объем вызвал падение надежности паразитного устройства NPN . С более чем 10 мА/мкм в 0,25 мкм производительность упала до менее половины в 28-нм CMOS.

Таким образом, для той же устойчивости к электростатическому разряду периметр необходимо удвоить.

Таким образом, для той же устойчивости к электростатическому разряду периметр необходимо удвоить. - Напряжение срабатывания Vt1 упало на каждом узле с ~6 В для 180-нм до ~4 В для 28-нм КМОП. Однако напряжение пробоя оксида с тонким затвором падало быстрее (>8 В до менее чем 3,5 В). С 90 нм, напряжение пробоя сток-подложка примерно такое же, как напряжение пробоя (тонкого) оксида. Это означает, что, например. 40-нанометровый зажим ggNMOS ESD больше не может защитить тонкий оксидный интерфейс , не говоря уже о самом себе.

- Инженеры по защите от электростатических разрядов придумали хитрые методы снижения напряжения срабатывания до напряжения удержания, например, с помощью объем или корпус или уклон ворот. Это отложило проблему.

- Напряжение ограничения также снижается на более продвинутых узлах CMOS (> 4 В до 3,5 В), но снижение происходит медленнее. В узле 28 нм напряжение фиксации выше, чем напряжение пробоя тонкого оксида .

Конец…

Конец…

Люди успешно использовали зажимы ggNMOS в 28-нм CMOS, например, в качестве зажимов CDM (вторичных). Благодаря короткой длительности импульса пробой оксида затвора в переходном режиме немного выше. Для основной или первичной защиты от электростатического разряда лучше полагаться на другие концепции защиты от электростатического разряда. Для интерфейсов на основе толстых оксидных транзисторов окно проектирования ESD по-прежнему достаточно велико. Большинство ячеек ввода-вывода общего назначения основаны на транзисторах с толстым оксидом.

Технология FinFET

Как и в случае с усовершенствованными CMOS, подход Snapback NMOS больше не является предпочтительным вариантом в процессах FinFET. Часто NMOS-транзистор не выдерживает обратного хода для импульсов TLP длительностью 100 нс, даже если стоки заблокированы силицидом. Транзистор FinFET NMOS не может защитить себя во время стресса от электростатического разряда. Пробой (тонкого) оксида затвора дополнительно снижается до 3 В или менее.

Окно проектирования ESD (для тонких оксидных интерфейсов) дополнительно сокращено в технологии FinFET. Транзистор snapback ggNMOS больше не эффективен.Проблемы возникают даже у интерфейсов на основе толстых оксидных транзисторов. Транзисторы NMOS FinFET с толстым оксидом также часто выходят из строя при возврате. К счастью, можно использовать и другие защитные устройства. Узнайте больше в другой статье нашего блога (защита от электростатического разряда для FinFET).

Высоковольтные и BCD-процессы

В высоковольтных и BCD-процессах разработчикам обязательно следует искать альтернативы. Крупные литейные заводы (по-прежнему) продвигают NLDMOS-транзисторы для защиты от электростатических разрядов в качестве ограничителя мощности, самозащитных драйверов и локальной защиты ввода-вывода. Конечно, разработчики интегральных схем, создающие сложные аналоговые схемы, часто полагаются на эти руководства и рекомендации.

Крупные литейные заводы (по-прежнему) продвигают NLDMOS-транзисторы для защиты от электростатических разрядов в качестве ограничителя мощности, самозащитных драйверов и локальной защиты ввода-вывода. Конечно, разработчики интегральных схем, создающие сложные аналоговые схемы, часто полагаются на эти руководства и рекомендации.

. седых волос. Единственная польза от этих литейных рекомендаций — это больше отладки/консалтинга для Sofics. Мы часто встречаем разработчиков микросхем, которые следовали рекомендациям производителя, но впоследствии сталкивались с проблемами электростатического разряда или защелкивания. Они протягивают руку и ожидают быстрого решения в течение 2 недель для повторного запуска своего следующего продукта.

Но отладка продуктов, связанных с электростатическим разрядом, не является нашей страстью. Наши инженеры предпочитают активно решать проблемы электростатического разряда . При каждой возможности тестирования чипа они ищут улучшенные концепции защиты, которые никто раньше не пробовал. Мы изобретаем, разрабатываем и оптимизируем решения для защиты от электростатического разряда, которые могут быть повторно использованы многими без необходимости повторного запуска продукта.

Наши инженеры предпочитают активно решать проблемы электростатического разряда . При каждой возможности тестирования чипа они ищут улучшенные концепции защиты, которые никто раньше не пробовал. Мы изобретаем, разрабатываем и оптимизируем решения для защиты от электростатического разряда, которые могут быть повторно использованы многими без необходимости повторного запуска продукта.

Кто прав?

Так что же происходит? Кто прав? Эксперты литейного производства по электростатическому разряду протестировали предлагаемые зажимы для защиты от электростатического разряда и с готовностью делятся результатами анализа TLP и HBM, чтобы продемонстрировать, что зажимам для защиты от электростатического разряда на основе NLDMOS можно доверять.

С другой стороны, компания Sofics смогла охарактеризовать свойства электростатического разряда транзисторов NLDMOS во многих процессах BCD на различных литейных заводах и собственных фабриках. Наш вывод состоит в том, что разработчикам микросхем следует воздерживаться от использования NLDMOS-транзисторов snapback для защиты от электростатических разрядов .

Разработка через тестирование