Транзисторный вентиль – Большая Энциклопедия Нефти и Газа, статья, страница 1

Транзисторный вентиль

Cтраница 1

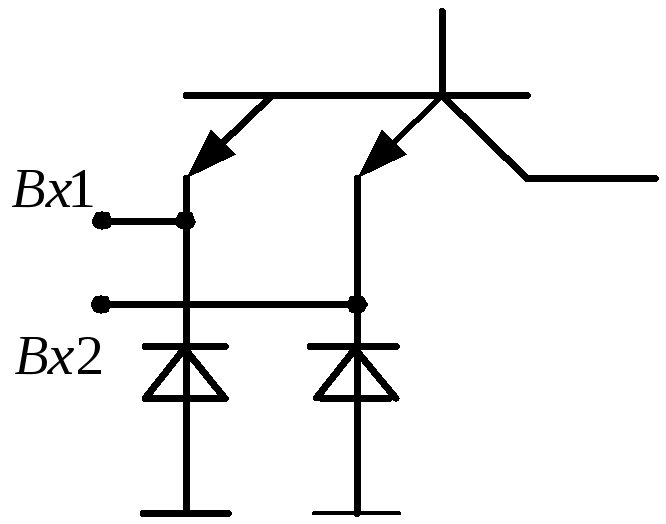

Простейшая схема транзисторного вентиля ИЛИ-НЕ показана на рис. 8.9. Эта схема использовалась в семействе логических элементов РТЛ ( резисторно-тран-зисторная логика), которые из-за низкой стоимости были популярны в 1960 – х годах, но в настоящее время они совершенно не употребляются. ВЫСОКИЙ уровень, действующий по любому входу ( или по обоим одновременно), откроет хотя бы один транзистор и на выходе возникнет НИЗКИЙ уровень. Поскольку по своей сути такой вентиль является инвертирующим, то для того, чтобы получить из него вентиль ИЛИ, к нему нужно добавить инвертор, как показано на рисунке. [1]

На рис. 8.9. показана простейшая схема транзисторного вентиля ИЛИ-НЕ. Эта схема использовалась в семействе логических элементов РТЛ ( резисторно-транзисторная логика), которые благодаря своей низкой стоимости были популярны в 1960 – х годах, однако в настоящее время полностью вышли из употребления. ВЫСОКИЙ уровень, действующий по любому входу ( или по обоим одновременно), откроет хотя бы один транзистор и на выходе возникает НИЗКИЙ уровень. Поскольку такой вентиль является инвертирующим по самой своей сути, то для того, чтобы получить из него вентиль ИЛИ, к нему нужно добавить инвертор, как показано на рисунке. [3]

Его основой является четырехразрядная микропроцессорная секция ( МПС), выполненная на прогрессивной биполярной технологии интегрально-инжекционной логики ( ИИЛ) и содержащая около 1500 транзисторных вентилей. [4]

Для этих вентилей в отличие от [5]

[5]

Страницы: 1

НОУ ИНТУИТ | Лекция | Неконстантные неисправности

Аннотация: Рассматриваются модели неисправностей не константного типа: замыкания, неисправности “транзистор постоянно открыт” и “транзистор постоянно закрыт”, задержки распространения сигналов, временные не исправности, функциональные неисправности, неисправности уровня ЯРП, перекрестные неисправности (crosstalk faults).

10.1 Замыкания

Неисправности типа замыкание имеют место в том случае, когда происходит соединение двух или более линий схемы и образуется “проводная логика” (wired logic) в месте возникшей электрической связи. Кратные замыкания (соединение больше двух линий) возникают обычно на внешних входах ИС. В настоящее время число дефектов, ведущих к замыканиям, увеличивается вследствие уменьшения размеров схем и увеличения плотности вентилей в кристалле. Очевидно, что число простых замыканий (между двумя линиями) в схеме, имеющей

Поведение логической схемы при замыкании зависит от технологии изготовления этой схемы. Например, в ТТЛ логике замыкание моделируется проводным И, как это показано на рис. 10.1.б).

Напротив, в случае ЭСЛ логики в месте замыкания реализуется проводное ИЛИ (рис. 10.1 в). Для КМОП технологии реализуемая при замыкании логическая функция зависит от типов логических вентилей и их характеристик по току.

Рис. 10.1. Проводная логика

Следует отметить, что дефекты замыкания могут вызвать функциональные изменения в логической схеме, которые нельзя представить традиционными моделями – неисправностями.

Рис. 10.2. Функциональные изменения вследствие замыкания.

Отметим, что замыкания могут преобразовывать комбинационные схемы в последовательностные. Например, замыкание в вентиле НЕ-ИЛИ, реализованного в КМОП технологии, может преобразовать этот вентиль в схему с памятью. К этому эффекту приводит также замыкание выхода вентиля со своим входом. При этом увеличивается число состояний последовательностной схемы.

10.2 Транзисторные неисправности (“устойчивый обрыв транзистора” и “устойчивое замыкание транзистора “)

Мы уже отмечали, что некоторые физические дефекты в КМОП технологии не могут быть представлены константными неисправностями. Основная причина заключается в том, что МОП комбинационные схемы не всегда остаются комбинационными при некоторых физических дефектах. Наиболее распространенными являются следующие виды отказов в МОП технологии: 1) обрыв и замыкание транзисторов; 2) обрывы между стоком, истоком и затвором; 3) короткие замыкания: исток – сток, затвор – сток, затвор – исток. Дефекты третьей группы обычно обусловлены пробоем оксида. Модели этих дефектов показаны на рис. 10.3 для МОП транзисторов вентилей с n

Рис. 10.3. Модели дефектов МОП-транзисторов

Такие неисправности называются “резистивными замыканиями”. Показано [10.3], что они могут моделироваться на уровне электрических схем сопротивлением для n-канальных транзисторов и сопротивлением и диодом для p-канальных транзисторов. Несмотря на то, что здесь величина сопротивления мала, часто эти дефекты являются непроверяемыми и на функциональном уровне схема ведет себя правильно.

При рассмотрении неисправностей для схем, выполненных по МОП технологии при моделировании транзистора полезно использовать модель “идеального ключа”. Тогда некоторые физические дефекты моделируются на переключательном уровне неисправностями типа ключ “постоянно открыт” или “постоянно закрыт”. Но, в общем случае, логический вентиль содержит несколько транзисторов (ключей). При данной модели предполагается, что только один транзистор (ключ) может быть “постоянно замкнут” (stuck-on – SON) или “постоянно открыт” (stuck-open -SOP). Покажем данные модели неисправностей на следующих примерах.

Рассмотрим неисправность типа SOP для вентиля НЕ-ИЛИ, выполненного по КМОП технологии, который представлен на рис. 10.4.

Здесь и – P-канальные МОП транзисторы, которые замкнуты при нулевых значениях входов , . При этих же значениях входов n-канальные транзисторы и разомкнуты. Таким образом, значения входов , соединяют выход вентиля с источником питания и изолируют его от земли (). Любое значение входов или соединяет выход вентиля с землей и изолирует его от источника питания (). Рассмотрим поведение этого вентиля при неисправности транзистор “постоянно разомкнут”.

Рис. 10.4. Неисправность транзистор “постоянно разомкнут”

При нулевых значениях входов , в неисправном вентиле только транзистор замкнут и выход вентиля изолирован (отсоединен) от источника питания. Транзисторы и при этом остаются разомкнутыми. Таким образом, при этой неисправности выход вентиля отсоединен и от источника питания и от земли, т.е. находится в отключенном состоянии (высокого импеданса) ∅. В реальной схеме выход имеет некоторый остаточный электрический заряд, скопившийся при предыдущих значениях входов, на паразитической емкости. Для обнаружения неисправности мы должны убедиться в том, что выход вентиля может поменять значение ∅ (состояние высокого импеданса) на 0. Это можно сделать путем инициализации первым набором , , который должен

у

становить выход (он обеспечивает разряд емкости на землю в неисправной схеме),

и дальнейшей подачей второго входного набора

,

, который исправную схему устанавливает в

, а неисправная остается в состоянии

.

Таким образом, полный тест для этой неисправности состоит из двух наборов входных значений

, которые в исправном вентиле производят выходной сигнал а в неисправном – . Алгоритмы генерации проверяющих тестов на переключательном уровне позволяют автоматизировать подобные процедуры [10.2].

В реальной схеме выход имеет некоторый остаточный электрический заряд, скопившийся при предыдущих значениях входов, на паразитической емкости. Для обнаружения неисправности мы должны убедиться в том, что выход вентиля может поменять значение ∅ (состояние высокого импеданса) на 0. Это можно сделать путем инициализации первым набором , , который должен

у

становить выход (он обеспечивает разряд емкости на землю в неисправной схеме),

и дальнейшей подачей второго входного набора

,

, который исправную схему устанавливает в

, а неисправная остается в состоянии

.

Таким образом, полный тест для этой неисправности состоит из двух наборов входных значений

, которые в исправном вентиле производят выходной сигнал а в неисправном – . Алгоритмы генерации проверяющих тестов на переключательном уровне позволяют автоматизировать подобные процедуры [10.2].

Следует отметить, что иногда можно и удобно использовать для подобных неисправностей модели вентильного уровня. Например, на рис. 10.5 представлена модель уровня вентилей для неисправностей только что рассмотренного элемента.

Рис. 10.5. Модели неисправностей КМОП-транзисторов вентильного уровня

Здесь последовательное соединение транзисторов (ключей) между выходом схемы и источником питания (или землей) заменяется вентилем И, а параллельное соединение – вентилем ИЛИ соответственно. Таким образом, транзисторы и моделируются вентилем И (с инверсными входами), а транзисторы и – вентилем ИЛИ. Выход этих вентилей в модели поступают на шину BUS, функционирование которой описывается табл. 10.1.

| 0 | 0 | ∅ |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 |

Далее рассмотрим неисправность типа SON на модели вентильного уровня рис. 10.4. На этой модели неисправность p-канального транзистора ( или ) “постоянно разомкнут” представляется константной неисправностью s-a-0 соответствующего входа вентиля И. Аналогично неисправность n-канального транзистора ( или ) типа SON представляется константной неисправностью s-a-1 соответствующего входа вентиля ИЛИ. Заметим, что на входном наборе , значение выхода исправной схемы , а неисправной – . Но s представляет замыкание между выходами вентилей и , при котором в неисправном состоянии течет большой ток, имеющий значение на несколько порядков больше чем в исправной схеме. Поэтому подобные неисправности можно обнаружить методами, основанными на измерении токов () [10.4].

Создан логический вентиль для теплового компьютера: Наука и техника: Lenta.ru

Ученые создали логические вентили для теплового компьютера. Вентили – основные элементы логической обработки данных – состоят из термических транзисторов, в которых носителем информации является наличие/отсутствие не электрического тока, а передачи тепла, сообщает PhysOrg.

В простейшем транзисторе обычного компьютера основным носителем информации является электрический ток: есть ток – транзистор находится в открытом состоянии, нет тока – в закрытом (на самом деле стандартный транзистор устроен чуть сложнее: состояние зависит от напряжения). В оптическом компьютере (такие уже созданы) функцию тока выполняет свет.

Профессор Баовэнь Ли (Baowen Li) и его коллеги из Национального университета Сингапура уже несколько лет работают над созданием еще одного типа компьютера, в котором носителем информации было бы тепло – тот вид энергии, который обычно считается в информационных технологиях бесполезным и даже вредным. Тепловой компьютер также называют “фононным”: в обычном компьютере информацию переносят электроны, в оптическом – фотоны, а в тепловом – фононы. Фононы – это квазичастицы, представляющие собой квант колебаний атомов твердого тела. С их помощью удобно описывать, в частности, передачу тепла.

Простейшим элементом теплового компьютера является термический транзистор, состоящий из трех точек (в обычных транзисторах точки называются электродами): две, определяющие состояние транзистора, особым образом соединены, третья – контрольная. Тепло в транзисторе передается колебаниями кристаллической решетки. Когда колебательные спектры двух точек перекрываются, между точками возникает устойчивый поток тепловой энергии (открытое состояние), когда не перекрываются – потока нет или он очень слаб (закрытое состояние).

Чтобы состояния были устойчивыми, система должна обладать особым свойством – малым тепловым откликом – большое изменение температуры должно вызывать малое изменение теплового потока. Сингапурская группа научилась делать такие системы в 2006 году.

На данный момент термические транзисторы позволяют оцифровывать тепловой сигнал, а также создавать вентили NOT (отрицание) и AND/OR (нестрогое ‘или’).

Исследователи утверждают, что потенциальный тепловой компьютер будет требовать сравнительно мало энергии и сможет питаться, например, остаточным теплом, производимым другими устройствами.

Using Electric 9-12: Logical Effort_ru

Using Electric 9-12: Logical Effort_ruЧасть 9: ИНСТРУМЕНТЫ

9-12: Логическая проба (Logical Effort) |

Инструмент логической пробы проверяет

цифровую схему и определяет оптимальный

размер транзистора для использования

в плане получения максимальной скорости.

Инструмент базируется на книге Logical

Effort, by Ivan Sutherland, Bob Sproull, and David Harris (Morgan

Kaufmann, San Francisco, 1999).

Когда логическая проба запущена, она помечает каждый цифровой вентиль схемы коэффициентом ветвления, который может использоваться для определения размера транзисторов внутри этого вентиля. Это сделано для разработчика (или, потенциально, для каких-то других средств), принимающего решение, использовать ли эту информацию в реальной компоновке IC.

Инструмент логической пробы имеет две функции: path analysis (анализ пути) и whole-facet analysis (полный анализ фасета).

В анализе пути пользователь должен

выбрать две точки в схеме, которые

определяют концы пути. Выбор этих двух

точек выполняется щелчком клавиши

selection по первой

точке, а затем клавишей toggle

select по второй. Емкостная нагрузка

на концах пути может быть задана созданием

объектов Load и параметризацией их емкости.

Эти объекты Load создаются субкомандой

New Arc Load команды Logical Effort меню

Tools. Для проведения анализа пути

используйте субкоманду Analyze Path,

которая определяет оптимальный

коэффициент ветвления для каждого шага

в пути. Кроме маркировки каждого вентиля

значением коэффициента ветвления

(показываемого в форме “h=2.5”),

вдоль пути отображаются значения

промежуточной емкости.

Кроме маркировки каждого вентиля

значением коэффициента ветвления

(показываемого в форме “h=2.5”),

вдоль пути отображаются значения

промежуточной емкости.

В полном анализе фасета (whole-facet analysis) инструмент логической пробы многократно предлагает емкостную нагрузку пока не определится коэффициент ветвления цепи. Заново емкости могут быть заданы субкомандой New Arc Load команды Logical Effort меню Tools. Тогда субкоманда Analyze Facet повторно проходит по цепи, пробуя найти коэффициент, который “меньше, чем” или “равен” максимальному усилению на каскад (первоначально 3). Как и в анализе пути, каждый вентиль маркируется значением коэффициента ветвления, и промежуточные емкости отображаются на схеме. Для изменения максимального усиления на каскад, используемого при полном анализе фасета, выполните субкоманду Logical Effort Options… команды Logical Effort меню Tools.

|

Помимо установки максимального усиления на каскад для полного анализа фасета субкоманда Logical Effort Options… команды Logical Effort меню Tools допускает другие установки. Вы можете запросить, чтобы значения промежуточной емкости не отображались после анализа, и вы можете запросить, чтобы анализируемые узлы были подсвечены. Также вы может установить пропорции проводников для каждой дуги (значение используется при вычислении нагрузки). |

Есть возможность переписать заданное

по умолчанию вычисление логической

пробы на единичном узле, для этого

используйте субкоманду Set Node Effort…

команды Logical Effort меню Tools. Введенное

значение показывается в форме “g=2″

на узле и используется при последующем

анализе.

Введенное

значение показывается в форме “g=2″

на узле и используется при последующем

анализе.

Пример Logical Effort может быть найден в библиотеке “samples.txt” (вы можете прочитать библиотеку субкомандой Readable Dump меню File). Отредактируйте фасет “tool-LogicalEffort” и используйте субкоманду Analyze Facet на нем.

Есть три команды, которые анализируют цепь в качестве дополнения к Logical Effort. Субкоманда Estimate Delays вычисляет фактор нагрузки для сети в фасете. Эта информация обычно не используется и предоставляется для будущих анализов Logical Effort. Субкоманда Show Network Loads переписывает каждую сеть в текущем фасете, показывая длину проводников, нагрузку и другую информацию. Субкоманда Analyze Network показывает детальный анализ текущей выбранной сети, включая информацию о площади и периметре вместе с информацией о нагрузке.

Отрицательное сопротивление может спасти графеновые транзисторы

Источники:

http://www.technologyreview.com/view/518426/how-to-save-the-troubled-gra…

http://compulenta.computerra.ru/veshestvo/materialovedenie/10008613/

Пока это только схема, но, кажется, её реализация позволит создать графеновые транзисторы, не ломая присущие этому материалу особенности об колено, а, напротив, используя их для производства более эффективной электроники.

Все помнят ситуацию с графеном? Десять лет отчаянной борьбы на переднем крае науки, а одно из главных обещанных достижений — графеновые транзисторы — пока скорее теория, чем практика. Ибо полупроводниковый транзистор требует запрещённой зоны, области значений энергии, которыми электрон в этом материале обладать не может. Без неё транзистор, что называется, не выключить. Увы, нормальный графен как проводник идеально анизотропен. Нет, есть, конечно, дисульфид молибдена с естественной запрещённой зоной. Но он как раз находится в самом начале развития.

Нет, есть, конечно, дисульфид молибдена с естественной запрещённой зоной. Но он как раз находится в самом начале развития.

Как только запрещённую зону в графене ни пытались создать: и складывали несколько слоев в один «бутерброд», и комбинировали с разными пластиками, и самое разное допирование применяли. Но итог плачевен: нужна ширина запрещённой зоны хотя бы в один электронвольт (при комнатной температуре), иначе приличного транзистора не будет. Получаются же пока только сотни миллиэлектронвольт, да и то ценой огромных токов утечки.

Гуаньсюн Лю (Guanxiong Liu) вместе с коллегами по Калифорнийскому университету в Риверсайде (среди которых два выходца из России) попробовал обойти проблему отсутствия запрещённой зоны таким образом, чтобы создать транзистор с переключением состояний совершенно нового типа.

Когда материал полупроводникового типа находится в состоянии изолятора, его можно переключить в проводящее состояние, придав небольшое количество энергии. Эта энергетическая разница двух состояний и называется шириной запрещённой зоны. Но вместо создания искусственной запрещённой зоны путём допирования и прочих ухищрений исследователи попробовали использовать явление отрицательного сопротивления для переключения состояний графенового транзистора.

Но сначала о том, что это такое. Отрицательное дифференциальное сопротивление — это явление, при котором ток, входя в материал, вызывает в нём падение напряжения вместо его интуитивно ожидаемого роста. Графен в определённых условиях, благодаря своей уникальной топологии, действительно горазд на такую особенность. Экспериментальной демонстрации отрицательного сопротивления в нормальных условиях посвящена значительная часть этой работы.

Но почему бы, спросили себя исследователи, это падение напряжения не использовать как одно из рабочих состояний, переключаясь таким образом не между проводящим и изолирующим состояниями, как нормальный транзистор, а между проводящим состоянием и состоянием отрицательного сопротивления?

В предложенной ими схеме три полевых транзистора на графене собираются в логический вентиль XOR (либо). Особо отметим, что обычный вентиль такого типа требует минимум восемь кремниевых транзисторов (на CMOS) и работает не быстрее буквально десятка гигагерц. В то же время, как заявляют авторы схемы, их тип XOR-вентиля функционирует на 400 ГГц — впрочем, как и более ранние графеновые транзисторы с высокими токами утечки.

Особо отметим, что обычный вентиль такого типа требует минимум восемь кремниевых транзисторов (на CMOS) и работает не быстрее буквально десятка гигагерц. В то же время, как заявляют авторы схемы, их тип XOR-вентиля функционирует на 400 ГГц — впрочем, как и более ранние графеновые транзисторы с высокими токами утечки.

Итак, налицо схема куда более компактного и радикально более быстрого вентиля, нежели обычные. Причём не работающего на классическом принципе «изолятор — проводник», а эксплуатирующего отрицательную дифференциальную проводимость. Увы, герои нашей заметки за эту работу пока не взялись. Кому-то надо построить такой вентиль и испытать его — причём, как нам кажется, сделать это стоит побыстрее. Ибо на столь «горячем» направлении конкуренты не дремлют.

Препринт исследования можно полистать здесь: http://arxiv.org/abs/1308.2931

Разбираем кварцевый генератор и его крохотную интегральную схему / Хабр

Кварцевый генератор – важный электронный компонент, обеспечивающий очень точную генерацию тактовой частоты за небольшие деньги. Из-за пьезоэлектрического эффекта его электрические свойства меняются в процессе вибрации. Поскольку можно сделать кристалл, который будет вибрировать с определённой частотой, кварцевые генераторы очень полезны для множества применений. Появились они в 1920-х, и сначала обеспечивали точную генерацию волн для радиостанций. В 1970-м году произошла революция наручных часов, когда в них стали использовать кварцевые генераторы высокой точности. Компьютеры, от ENIAC 1940-х годов и до сей поры используют кварцевые генераторы для генерации тактовой частоты.

В современных ПК всё ещё используются кварцевые генераторы, но для получения многогигагерцовых тактовых частот применяются более сложные технологии. ПК использует кристалл с частотой гораздо меньшей, чем рабочая, и умножает её при помощи фазовой автоподстройки частоты. Компьютеры часто используют кристалл на 14 318, поскольку эту частоту использовали в старых телевизорах, и такие кристаллы были недорогими и широко распространёнными.

Для того, чтобы кристалл вибрировал, его схеме требуются дополнительные компоненты. В 1970-х набрали популярность модульные кварцевые генераторы – в этих компактных и лёгких в использовании микросборках комбинировались сам кристалл, ИС и дискретные компоненты. Мне стало интересно, как работает один из таких модулей, поэтому я вскрыл один из них и провёл реверс-инжиниринг его чипа. В данном посте я расскажу, как он работает, и опишу крохотную КМОП-схему, им управляющую. Оказалось, что внутри модуля происходит больше интересного, чем можно было ожидать.

Модуль генератора

Я изучал модуль от карточки для IBM PC. Модуль находится в прямоугольном металлическом корпусе с 4-мя контактами, защищающем электронику от электрического шума (это Rasco Plus в прямоугольном корпусе справа на фото, а не квадратная ИС от IBM). Модуль генерирует сигнал в 4,7174 МГц, что следует из надписи на его корпусе.

Почему же карточка использует кристалл с такой необычной частотой — 4,7174 МГц? В 1970-х IBM 3270 был очень популярным терминалом с ЭЛТ. Терминалы соединялись коаксиальным кабелем и использовали протокол Interface Display System Standard, работавший с тактовой частотой в 2,3587 МГц. В конце 1980-х IBM производила интерфейсные карточки для подсоединения IBM PC к сети 3270. Мой кристалл как раз с одной из таких карточек (тип 56X4927), и частота кристалла равняется 4,7174 МГц – ровно в два раза больше, чем 2,3587 МГц.

Модуль кварцевого генератора находится справа внизу. Надпись на корпусе: Rasco Plus. 4.7174 MHZ, Motorola 1987. Квадратный модуль слева – это ИС от IBM.

Я вскрыл корпус модуля, чтобы посмотреть на его гибридную схему. Я ожидал увидеть там кварцевый кристалл, напоминающий драгоценный камень в шкатулке, однако обнаружил, что кварцевые генераторы используют очень тонкий кварцевый диск. Я повредил его при вскрытии, поэтому у него не хватает кусочка справа вверху. Он виден в левой части фото – с двух сторон к нему подходят металлические электроды. Те, в свою очередь, соединяются с небольшими штырьками, на которых кристалл поднят над поверхностью корпуса, чтобы он мог свободно вибрировать.

Те, в свою очередь, соединяются с небольшими штырьками, на которых кристалл поднят над поверхностью корпуса, чтобы он мог свободно вибрировать.

Внутри корпуса кварцевого генератора – компоненты, закреплённые на керамической подложке. Они подсоединяются к схеме крохотной золотой проволочной разваркой. Конденсатор на 3 нФ и плёночный резистор на 10 Ом, расположенные на подложке методом поверхностного монтажа, отфильтровывают шум, поступающий от контакта питания.

Схема работы ИС

На фото ниже показан крохотный кристалл ИС под микроскопом. Размечены контактные площадки и основные функциональные блоки. Зелёно-коричневые участки – это кремний, формирующий ИС. Жёлтоватый металлический слой соединяет компоненты с ИС. Под металлом находится красноватый слой поликремния, где формируются транзисторы – но он практически полностью закрыт металлическим слоем. По краям чипа расположена проволочная разварка, подсоединённая к контактным площадкам, соединяющим чип с остальными частями модуля. Две площадки (select и disable) не подсоединены. Чип произведён компанией Motorola в 1986. По артикулу SC380003 информации я не нашёл.

Кристалл ИС с разметкой основных блоков. «FF» обозначает триггеры. «sel» – контактные площадки [select pads]. «cap» – площадки, подсоединённые к внутренним конденсаторам.

У ИС есть две задачи. Во-первых, её аналоговые компоненты заставляют кристалл колебаться. Во-вторых, её цифровые компоненты делят частоту на 1, 2, 4 или 8, и выдают сигнал тактовой частоты с большим током (делитель задаётся двумя контактами выбора на ИС).

Кварцевый генератор реализован по приведённой ниже схеме, которая называется “генератор Колпитца”. Она сложнее обычной схемы кварцевого генератора. Суть в том, что кристалл и два конденсатора колеблются с заданной частотой. Однако колебания быстро затухли бы, если бы не поддерживающая обратная связь с поддерживающего транзистора.

Типичный кварцевый генератор строится по простой схеме под названием «генератор Пирса», в которой из кристалла и инвертера формируется цепь обратной связи. Два заземлённых конденсатора в середине делают её очень похожей на классический генератор Колпитца.

Два заземлённых конденсатора в середине делают её очень похожей на классический генератор Колпитца.

Не уверен, по какой причине разобранный мною кварцевый генератор использует более сложную схему, которая требует хитрого смещения напряжения.

В 1918 году Эдвин Колпитц, главный исследователь в компании Western Electric, изобрёл кварцевый генератор на катушке индуктивности и конденсаторе. Сегодня эта схема известна, как генератор Колпитца. Идея в том, что катушка индуктивности с конденсатором формируют «резонансный резервуар», колеблющийся с частотой, зависящей от характеристик компонентов. Можно представлять, что электричество в этом резервуаре как бы плещется туда и сюда между катушкой индуктивности и конденсаторами. Сами по себе колебания быстро затухли бы, поэтому для их подпитки используется усилитель. В оригинальном генераторе Колпитца усилителем была электронная лампа. Позднее схемы перешли на транзисторы, но этот усилитель может быть операционным или другого типа. В других схемах конец заземляется, чтобы в середине шла обратная связь. Тогда конденсаторы ничего не инвертируют, поэтому используется не инвертирующий усилитель.

Упрощённая схема генератора Колпитца с базовыми компонентами.

Ключевая особенность генератора Колпитца заключается в двух конденсаторах, формирующих делитель напряжения. Поскольку они в середине заземлены, на двух концах у них будет напряжение противоположных значений: когда одно повышается, второе понижается. Усилитель берёт сигнал с одного конца, усиливает его, и подаёт на другой. Усилитель инвертирует сигнал, а конденсаторы дают второе инвертирование, так, что обратная связь усиливает оригинальный сигнал (обеспечивая фазовый сдвиг на 360°).

В 1923 году Джордж Вашингтон Пирс, профессор физики в Гарварде, заменил катушку индуктивности в генераторе Колпитца на кристалл. Благодаря этому генератор стал более точным, и его стали широко использовать в радиопередатчиках и других устройствах. Пирс запатентовал своё изобретение и заработал приличные деньги на таких компаниях, как RCA и AT&T. Наличие патентов привело к многолетним судебным тяжбам, дошедшим в итоге до Верховного суда.

Наличие патентов привело к многолетним судебным тяжбам, дошедшим в итоге до Верховного суда.

Несколько десятилетий генератор Пирса было принято называть генератором Колпитца с кристаллом. В генераторе Пирса часто отсутствовали характерные конденсаторы, вместо которых использовалось паразитная ёмкость электронной лампы. Терминология постепенно менялась, и два разных типа кварцевых генератора начали называть генератором Колпитца (с конденсаторами) и генератором Пирса (без них).

Ещё одно изменение терминологии произошло в связи с тем, что генератор Колпитца, генератор Пирса и генератор Клаппа были топологически идентичными кварцевыми генераторами, отличавшимися только в том, какая часть схемы считалась землёй (коллектор, эмиттер или база соответственно). Все эти генераторы можно называть генераторами Колпитца, только с общим коллектором, общим эмиттером или общей базой.

Этот экскурс в историю я сделал с тем, чтобы показать, что в различных источниках эти генераторы называют по-разному, генераторами Колпитца или Пирса, причём противоречивым образом. Тот генератор, что изучал я, можно назвать генератором Колпитца с общим стоком (по аналогии с общим коллектором). Также его можно назвать генератором Колпитца на основании расположения заземления. Но исторически его можно назвать генератором Пирса, поскольку он использует кристалл. Также он называется кварцевым генератором с одним контактом, поскольку только один контакт кристалла подсоединён к внешней схеме (другой заземлён).

Упрощённая схема генератора

Увеличение напряжения на кристалле включает транзистор, ток идёт в конденсаторы, увеличивая напряжение на них (и на кристалле). Уменьшение напряжения на кристалле выключает транзистор, сток тока (кружок со стрелкой) вытягивает ток из конденсаторов, уменьшая напряжение на кристалле. Таким образом, обратная связь с транзистора усиливает колебания кристалла, поддерживая их.

Цепи напряжения смещения и тока являются важной частью этой схемы. Напряжение смещения устанавливает вентиль транзистора где-то посередине между включённым и выключенным состоянием, поэтому колебания напряжения на кристалле включают его и выключают. Ток смещения находится посередине между значениями токов включённого и выключенного транзистора, поэтому ток, приходящий и уходящий из конденсаторов, сбалансирован (я упрощаю, говоря о включённых и выключенных состояниях – в реальности сигнал будет иметь синусоидальную форму).

Напряжение смещения устанавливает вентиль транзистора где-то посередине между включённым и выключенным состоянием, поэтому колебания напряжения на кристалле включают его и выключают. Ток смещения находится посередине между значениями токов включённого и выключенного транзистора, поэтому ток, приходящий и уходящий из конденсаторов, сбалансирован (я упрощаю, говоря о включённых и выключенных состояниях – в реальности сигнал будет иметь синусоидальную форму).

Цепи напряжения смещения и тока – это умеренно сложные аналоговые схемы, состоящие из кучки транзисторов и нескольких резисторов. Подробно описывать их не буду, скажу лишь, что они используют цепи обратной связи для генерации нужных фиксированных значений напряжения и тока.

Значительную часть ИС занимают пять конденсаторов. На схеме один расположен сверху, три идут параллельно, формируя нижний конденсатор на схеме, а один стабилизирует цепь напряжения смещения. На фото кристалла ниже показан один из конденсаторов после растворения верхнего металлического слоя. Красные и зелёные участки – это поликремний, формирующий верхнюю пластину конденсатора вместе с металлическим слоем. Расположенный под поликремнием розоватый участок – вероятно, нитрид кремния, формирующий диэлектрический слой. Кремний с добавками, которого на фото не видно, формирует нижнюю пластину конденсатора.

Конденсатор на кристалле. Большой бледный квадрат слева – площадка для подсоединения проволочной разварки к ИС. Сложные структуры слева – фиксирующие диоды контактов. Похожие на клевер структуры справа – это транзисторы.

Интересно, что конденсаторы на чипе не соединяются вместе. Они подсоединены к трём площадкам, связанным между собой проволочной разваркой. Возможно, это придаёт схеме гибкость – ёмкость цепи можно изменить, удалив проводник, ведущий к конденсатору.

Цифровая схема

С правой части чипа находится цифровая схема делителя выходной частоты кристалла на 1, 2, 4 или 8. Благодаря ей один и тот же кристалл может выдавать четыре частоты.

Делитель составлен из трёх триггеров, подключённых последовательно. Каждый делит входящий импульс пополам. Мультиплексор 4 к 1 выбирает между оригинальной частотой импульсов или выходом с одного из триггеров. Выбор осуществляется при помощи проводников, подходящих к двум площадкам для выбора с правой части кристалла. Итоговая частота фиксируется на этапе производства. Для декодирования контактов и генерации четырёх управляющих сигналов мультиплексору и триггерам используются четыре вентиля NAND вместе с инверторами.

Делитель составлен из трёх триггеров, подключённых последовательно. Каждый делит входящий импульс пополам. Мультиплексор 4 к 1 выбирает между оригинальной частотой импульсов или выходом с одного из триггеров. Выбор осуществляется при помощи проводников, подходящих к двум площадкам для выбора с правой части кристалла. Итоговая частота фиксируется на этапе производства. Для декодирования контактов и генерации четырёх управляющих сигналов мультиплексору и триггерам используются четыре вентиля NAND вместе с инверторами.Реализация логики КМОП

Кип построен на логике КМОП (комплементарная структура металл-оксид-полупроводник). Она использует совместно работающие транзисторы двух типов, N-МОП и P-МОП. На диаграмме ниже показано устройство N-МОП транзистора. Транзистор можно считать переключателем между истоком и стоком, который контролирует вентиль. Исток и сток (зелёные) состоят из участков кремния с добавками, меняющими его полупроводниковые свойства – из N+ кремния. Вентиль сделан из особого кремния, поликремния, отделённого от кремниевой подложки очень тонким изолирующим слоем оксидным слоем. N-МОП транзистор включается, когда вентиль подтягивается вверх.

Структура N-МОП транзистора. Структура P-МОП транзистора похожа, однако участки кремния N- и P-типа меняются местами.

Строение P-МОП транзистора противоположно N-МОП: исток и сток состоят из P+ кремния, включённого в N кремний. Работает он тоже противоположно N-МОП транзистору: включается, когда вентиль подтягивается вниз. Обычно P-МОП транзисторы подтягивают сток вверх, а N-МОП – вниз. В КМОП транзисторы работают, дополняя друг друга, подтягивая выходной сигнал вверх или вниз по необходимости.

На диаграмме ниже показано, как в КМОП реализован вентиль NAND. Если на вход подать 0, соответствующий P-МОП транзистор (вверху) включится и притянет выход вверх. Если на оба входа подать 1, N-МОП транзистор (внизу) включится и подтянет выход вниз. Таким образом схема реализует функцию NAND.

На диаграмме ниже показано, как NAND-вентиль выглядит на кристалле. В отличие от изображений в учебниках, у реальных транзисторов бывает сложная, извилистая форма. С левой стороны находятся P-МОП транзистор, а с правой – N-МОП. Красноватые дорожки над кремнием – это поликремний, формирующий вентили. Большая часть кремния в подложке благодаря добавкам проводит ток, и выглядит чуть темнее непроводящего кремния без добавок с левого и правого краёв, а также в центре. Для изготовления этого фото металлический слой был вытравлен. Жёлтые линии обозначают места, где раньше были металлические проводники. Кружочки — это связи металлического слоя с нижними слоями, кремния или поликремния.

Как NAND-вентиль выглядит на кристалле

Транзистор на фото можно сопоставить со схемой NAND-вентиля. Посмотрите на сформированные поликремнием вентили транзистора, и на то, что они разделяют. От участка +5 есть дорожка к выходу через длинный P-МОП транзистор слева. Второй путь идёт через небольшой P-МОП транзистор в центре – это показывает, что транзисторы подключены параллельно. Каждый вентиль контролирует один из входов. Слева дорожка от земли к выходу должна пойти через оба концентрических N-МОП транзистора – они подключены последовательно.

В этой ИС также используется много транзисторов с кольцевыми вентилями. Эта необычная техника расположения элементов позволяет с большой плотностью разместить множество параллельных транзисторов. На фото ниже показано 16 транзисторов с кольцевыми вентилями. Похожие на клевер узоры медного цвета – это сток транзисторов, а снаружи находится исток. Металлический слой (тут он удалён) объединяет соответственно все истоки, вентили и стоки. Параллельные транзисторы работают как один большой. Параллельные транзисторы используются для подачи больших токов на выход. В схеме смещения вместе соединяются различное количество транзисторов (6, 16 или 40), чтобы получать нужное соотношение токов.

Передаточный вентиль

Ещё одна ключевая схема чипа – это передаточный вентиль.

Он работает как переключатель, через который сигнал либо проходит, либо нет. На схеме ниже показано, как передаточный вентиль делается из двух транзисторов, N-МОП транзистора и P-МОП транзистора. Если по линии enable подаётся большое напряжение, включаются оба транзистора, и входной сигнал проходит на выход. Если напряжение низкое, они выключаются, блокируя сигнал. Справа показано условное обозначение передаточного вентиля на схемах.

Он работает как переключатель, через который сигнал либо проходит, либо нет. На схеме ниже показано, как передаточный вентиль делается из двух транзисторов, N-МОП транзистора и P-МОП транзистора. Если по линии enable подаётся большое напряжение, включаются оба транзистора, и входной сигнал проходит на выход. Если напряжение низкое, они выключаются, блокируя сигнал. Справа показано условное обозначение передаточного вентиля на схемах.Мультиплексор

Мультиплексор используется для выбора одного из четырёх тактовых сигналов. На диаграмме ниже показано, как мультиплексор реализован на основе передаточных вентилей. Мультиплексор принимает на вход четыре сигнала: A, B, C и D. Один из входов выбирается через активацию соответствующей линии выбора и её дополнения. Этот вход связывается через передаточный вентиль с выходом, а другие входы блокируются. Хотя мультиплексор можно построить и на стандартных логических вентилях, его реализация на передаточных вентилях получается эффективнее.

Мультиплексор 4 к 1 на основе передаточных вентилей

На схеме ниже показаны транзисторы, из которых состоит мультиплексор. Ко входам B и С подключено по паре транзисторов. Думаю, это сделано потому, что у пары транзисторов сопротивление получается половинным. Поскольку входы В и С предназначены для высокочастотных сигналов, пара транзистора позволяет уменьшить задержки и искажения.

На фото ниже показано, как мультиплексор реализован на кристалле физически. Лучше всего видно поликремниевые вентили. Металлический слой удалён. Металлические проводники шли вертикально, соединяя соответствующие сегменты транзисторов. Истоки и стоки соседних транзисторов объединены в единые участки, расположенные между вентилями. В верхнем прямоугольнике находятся N-МОП транзисторы, а в нижнем – P-МОП. Поскольку P-МОП транзисторы менее эффективны, нижний прямоугольник должен быть больше.

Триггер

На чипе есть три триггера, делящие тактовую частоту.

Кварцевый генератор использует переключаемые триггеры, которые переключаются между 0 и 1 каждый раз, когда получают входящий импульс. Поскольку два входящих импульса дают один исходящий (0→1→0), триггер делит частоту пополам.

Кварцевый генератор использует переключаемые триггеры, которые переключаются между 0 и 1 каждый раз, когда получают входящий импульс. Поскольку два входящих импульса дают один исходящий (0→1→0), триггер делит частоту пополам.Триггер состоит из передаточных вентилей, инверторов и NAND-вентиля – см. схему ниже. Когда входящий тактовый сигнал равен 1, выход проходит через инвертор и первый передаточный вентиль в точку А. Когда входящий сигнал переключается на 0, открывается первый передаточный вентиль, и в точке А остаётся предыдущее значение. Тем временем закрывается второй передаточный вентиль, поэтому сигнал проходит через второй инвертор и передаточный вентиль в точку В. NAND-вентиль снова его инвертирует, в результате чего значение выхода меняется на противоположное. Второй цикл входящего сигнала тактовой частоты повторяет этот процесс, благодаря чему выход возвращается к изначальному значению. В итоге два цикла входящих сигналов дают один цикл выходящего сигнала, так что триггер делит частоту на 2.

У каждого триггера есть разрешающий вход. Если триггер для выбранного выхода не нужен, он отключается. К примеру, если выбирается режим деления на 2, используется только первый триггер, а два другие отключаются. Полагаю, это делается для уменьшения энергопотребления. Это не зависит от контакта отключения на модуле, который полностью блокирует выходящий сигнал. Это отключаемое свойство опционально; в данном модуле такой функции нет, а контакт отключения не подключен к ИС.

На схеме выше инвертеры и передаточные вентили показаны в виде отдельных структур. Однако в триггере используется интересная структура вентилей, комбинирующая инвертер и передаточный вентиль (слева) в единый вентиль (справа). Пара транзисторов, подключенных к data in, работают как инвертер. Однако если сигнал тактовой частоты нулевой, питание и земля блокируются, и вентиль не влияет на выход, сохраняя предыдущее напряжение. Так работает передаточный вентиль.

Комбинированные инвертер и передаточный вентиль

На фото ниже показано, как один из таких вентилей выполнен на кристалле. На фото видно металлический слой сверху. Под ним видно красноватые вентили из поликремния. Слева расположены два P-МОП транзистора в виде концентрических кругов. Справа находятся N-МОП транзисторы.

На фото видно металлический слой сверху. Под ним видно красноватые вентили из поликремния. Слева расположены два P-МОП транзистора в виде концентрических кругов. Справа находятся N-МОП транзисторы.

Заключение

Хотя модуль кварцевого генератора снаружи кажется простым, внутри него больше компонентов, чем можно было бы ожидать. Там находится не только кристалл кварца, но и дискретные компоненты, и крохотная ИС. В ИС скомбинированы конденсаторы, аналоговые цепи, обеспечивающие колебания, и цифровые цепи для выбора частоты. Можно выбрать одну из четырёх частот, изменяя проводку ИС на этапе производства.

Больше информации по кварцевым генераторам можно найти на сайтах EEVblog, electronupdate и WizardTim. Про генератор Колпитца можно посмотреть на Hackaday.

Закончу фотографией чипа после удаления слоёв металла и оксида, чтобы было видно кремний и поликремний. Больше всего выделяются крупные розоватые конденсаторы, однако можно рассмотреть и транзисторы.

Кликабельно

виды, устройство, схемы, описание работы

Что такое ключ на транзисторах?

Ключи на полевых транзисторах широко используются для коммутации аналоговых и цифровых сигналов.

В аналоговых ключах обычно используют транзисторы с управляющим p-n-переходом или МДП-транзисторы с индуцированным каналом. В цифровых ключах обычно используют МДП-транзисторы с индуцированным каналом. В последнее время полевые транзисторы все чаще используют в силовой импульсной электронике.

Ключи на полевых транзисторах отличаются малым остаточным напряжением. Они могут коммутировать слабые сигналы (в единицы микровольт и меньше). Это следствие того, что выходные характеристики полевых транзисторов проходят через начало координат.

Васильев Дмитрий Петрович

Профессор электротехники СПбГПУ

Задать вопрос

Для примера изобразим выходные характеристики транзистора с управляющим переходом и каналом p-типа в области, прилегающей к началу координат (рис. 3.17). Обратим внимание, что характеристики в третьем квадранте соответствуют заданным напряжениям между затвором и стоком.

3.17). Обратим внимание, что характеристики в третьем квадранте соответствуют заданным напряжениям между затвором и стоком.

Однако минимальное сопротивление включенного ключа на полевом транзисторе может быть больше, чем ключа на биполярном транзисторе (т. е. наклон самой круто поднимающейся характеристики полевого транзистора может быть меньше, чем наклон соответствующей характеристики на биполярном транзисторе). Поэтому при значительном токе падение напряжения на полевом транзисторе может быть больше, чем падение напряжения на биполярном транзисторе.

Иногда остаточным напряжением на ключе называют не то напряжение, которое соответствует нулевому току, а то, которое соответствует некоторому значительному току ключа.

Это нужно иметь в виду, чтобы понять смысл на первый взгляд парадоксального утверждения, встречающегося у некоторых авторов и состоящего в том, что остаточное напряжение ключей на полевых транзисторах больше, чем ключей на биполярных транзисторах, и поэтому «полевой транзистор обладает худшими ключевыми свойствами по сравнению с биполярным».

Орлов Анатолий Владимирович

Начальник службы РЗиА Новгородских электрических сетей

Задать вопрос

Кстати нужно сказать, что наличие подобных на первый взгляд противоречивых утверждений полезно воспринимать как знак того, что выбор конкретного решения (в данном случае выбор для коммутации полевого или биполярного транзистора) следует осуществлять на основе всестороннего анализа.

В статическом состоянии ключ на полевом транзисторе потребляет очень малый ток управления. Однако этот ток увеличивается при увеличении частоты переключения. Очень большое входное сопротивление ключей на полевых транзисторах фактически обеспечивает гальваническую развязку входных и выходных цепей.

Это позволяет обойтись без трансформаторов в цепях управления. Ключи на полевых транзисторах часто менее быстродействующие в сравнении с ключами на биполярных транзисторах.

Схема цифрового ключа на МДП-транзисторе с индуцированным каналом n-типа

Изобразим схему цифрового ключа на МДП-транзисторе с индуцированным каналом n-типа и резистивной нагрузкой и соответствующие временные диаграммы (рис. 3.18).

На схеме изображена емкость нагрузки Сн, моделирующая емкость устройств, подключенных к транзисторному ключу. Очевидно, что при нулевом входном сигнале транзистор заперт и uси= Eс. Если напряжение uвх больше порогового напряжения Uзи.порог транзистора, то он открывается и напряжение uси уменьшается.

Абрамян Евгений Павлович

Доцент кафедры электротехники СПбГПУ

Задать вопрос

Ключи на полевых транзисторах с управляющим p-n-переходом входят в состав различных микросхем серий 284, 504 и др.

Напряжение на ключе в его включенном состоянии Uвкл зависит от сопротивления стока Rc, величины входного сигнала и особенностей стоковых характеристик транзистора. Скорость изменения напряжения на выходе определяется сопротивлением Rc, емкостью Сн и частотными свойствами транзистора.

Схема цифрового ключа на МДП-транзисторе с нагрузочным МДП-транзистором

Изобразим схему цифрового ключа на МДП-транзисторе с нагрузочным МДП-транзистором (с динамической нагрузкой) (рис. 3.19). Отметим, что при использовании интегральной технологии такой ключ, как ни странно на первый взгляд, изготовить проще в сравнении с рассмотренным выше (ССЫЛКА), имеющим нагрузочный резистор. Транзистор Т1 называют активным, а транзисторТ2 — нагрузочным.

Вначале рассмотрим закрытое состояние ключа. При этом uвх < Uзи.nopoгl , где Uзи.nopoгl — пороговое напряжение для транзистора T1. В этом случае транзистор Т1 закрыт и через оба транзистора протекает очень малый ток (обычно не более 1 нА). При этом напряжение uси1близко к напряжению Ес, а напряжение uси1 близко к нулю.

В рассматриваемом состоянии транзисторТ2 также закрыт, хотя напряжение между затвором и истоком этого транзистора положительно (очевидно, что uзи2 = uси2). Но соотношение между параметрами транзисторов обеспечивается именно такое, чтобы в закрытом состоянии ключа выполнялось соотношение uси1= Ес.

По крайней мере очевидно, что напряжение uси2не может быть больше порогового напряжения Uзu.nopoг2 для транзистора Т2, иначе бы транзистор Т2 открылся и напряжение на нем уменьшилось.

Теперь рассмотрим открытое состояние ключа. При этом uвх> uзи.порог1. Транзистор Т1 открыт и напряжение uси1 близко к нулю, а напряжение на транзисторе Т2 близко к напряжению питания.

В рассматриваемом состоянии транзистор Т2 также открыт, при этом uзи2= uси2= Ес. Но транзисторы конструируют таким образом, чтобы удельная крутизна транзистора Т2 была намного меньше, чем удельная крутизна транзистора T1 .Именно поэтому в открытом состоянии ключа uси1 = 0 (часто это напряжение лежит в пределах 50…100 мВ). Так как удельная крутизна транзистора Т2 мала, ток, протекающий через открытый ключ, сравнительно мал.

Схема цифрового ключа на комплементарных МДП-транзисторах

Изобразим схему цифрового ключа на комплементарных МДП-транзисторах (комплементарный МДП-ключ, КМОП-ключ) (рис. 3.20).

Здесь использованы взаимодополняющие друг друга (комплементарные) транзисторы: транзистор Т, с каналом n-типа и транзистор Т2 с каналом p-типа. Обозначим через Uзи.порог1 и Uзи.порог2 пороговые напряжения для транзисторов соответственно Т1 и Т2. Стоит обратить внимание, что каждое из указанных пороговых напряжений является положительным.

Пусть uвх= 0, тогда, очевидно, транзистор T1 закрыт, а транзистор Т2 открыт. При этом uсн1= Ес, uис2= 0. Если uвх> Uзи.порогl, тогда транзистор Т1 открыт. Пусть, кроме того, uвх> Ес — Uзи.порог2, тогда транзистор Т2 закрыт. При этом uси1= 0, uис2= Ес.

Надо отметить, что если Ес < Uзи.порог1 + Uзи.порог2, то при изменении входного сигнала не возникает ситуация, когда оба транзистора включены. Но если данное неравенство не выполняется, то такая ситуация будет иметь место при некотором промежуточном напряжении uвх, и тогда через транзисторы протекает так называемый сквозной ток.

Васильев Дмитрий Петрович

Профессор электротехники СПбГПУ

Задать вопрос

Если длительность переднего фронта и длительность среза (заднего фронта) входного импульса мала, то сквозной ток протекает короткое время, но и в этом случае он оказывает негативное влияние на работу схемы.

Как следует из изложенного, в каждом из двух установившихся режимов, т. е. и в открытом, и в закрытом состоянии, ключ практически не потребляет ток от источника питания. Это первое важное достоинство комплементарного ключа.

Вторым важным достоинством комплементарного ключа является резкое отличие выходного напряжения в открытом состоянии ключа (единицы микровольт и менее) и выходного напряжения в закрытом состоянии (это напряжение меньше напряжения питания всего лишь на единицы микровольт и менее). Это обеспечивает высокую помехоустойчивость цифровых схем на комплементарных ключах.

Третьим важным достоинством комплементарного ключа является его повышенное быстродействие. Оно может быть на порядок больше, чем у двух других ранее изученных ключей на полевых транзисторах. Повышенное быстродействие объясняется тем, что как разряд емкости Сн, так и ее заряд происходит через соответствующий открытый транзистор (емкость разряжается через транзистор T1 и заряжается через транзистор Т2).

При этом в начале заряда или разряда через соответствующий транзистор протекает большой ток, который быстро изменяет напряжение емкости. Естественно предположить, что входной сигнал поступает от такого же ключа, т. е. или uвх= , или uвх= Ес. В этом случае, чем больше напряжение питания Ес, тем больше отпирающий сигнал на соответствующем транзисторе и тем больше его начальный ток (к примеру, при uвх= 0, uиз2= Ес).

Поэтому при увеличении напряжения питания быстродействие комплементарного ключа увеличивается.

Описанные достоинства, а также отработанность технологии изготовления явились причиной широкого использования КМОП-ключей.

Рассмотрим простейшую схему аналогового ключа на МДП-транзисторе (рис. 3.21).

Эта схема получается из предыдущей при замене транзистора Т1 резистором нагрузки, а источника питания — источником входного сигнала.

Абрамян Евгений Павлович

Доцент кафедры электротехники СПбГПУ

Задать вопрос

Подложка транзистора подключена к положительному полюсу источника питания, т. е. к точке с наибольшим потенциалом, для того чтобы p-n-переходы между подложкой и истоком и подложкой и стоком не открывались.

Транзистор этого аналогового ключа работает подобно тому, как работает транзистор Т2 рассмотренного комплементарного ключа. Например, для отпирания транзистора необходимо, чтобы напряжение uупр было малым.

Ключ может коммутировать как положительное, так и отрицательное входное напряжение.

Двунаправленный аналоговый ключ (передающий вентиль) на комплементарных транзисторах

Рассмотрим теперь двунаправленный аналоговый ключ (передающий вентиль) на комплементарных транзисторах (рис. 3.22).

Ключ предназначен для передачи напряжения uас вывода А на вывод В или напряжение ub с вывода В на вывод А. Предполагается, что эти напряжения находятся в пределах от 0 до +Еn. Транзисторы Т1 и Т2 образуют рассмотренный выше комплементарный ключ. Двунаправленный ключ открыт, когда uупр= +Еn. В этом случае по крайней мере один из транзисторов Т3 и Т4 открыт. Ключ закрыт, когда uупр= 0.

Абрамян Евгений Павлович

Доцент кафедры электротехники СПбГПУ

Задать вопрос

Если схему изменить и на затворы транзисторов Т3 и Т4 подавать не только положительные, но и отрицательные напряжения, то ключ будет в состоянии работать не только при положительных, но и отрицательных напряжениях uа и ub.

Ключи на полевых транзисторах с изолированным затвором входят в состав микросхем серий 168, 547 и др., а на комплементарных транзисторах — в состав микросхем серий 590, 591, 176, 561, 1564.

Проектирование логического элемента И с использованием транзисторов

Как многие из нас знают, интегральная схема или ИС – это комбинация множества небольших схем в небольшом корпусе, которые вместе выполняют командную задачу. Подобно операционному усилителю или микросхеме таймера 555, она построена на основе комбинации многих транзисторов, триггеров, логических вентилей и других комбинационных цифровых схем. Точно так же триггер может быть построен с использованием комбинации логических вентилей, а сам логический вентиль может быть построен с использованием нескольких транзисторов.

Логические вентили– это основа многих цифровых электронных схем. От базовых триггеров до микроконтроллеров. Логические вентили образуют основной принцип хранения и обработки битов. Они устанавливают отношения между каждым вводом и выводом системы с использованием логики артметики. Есть много разных типов логических вентилей, и каждый из них имеет разную логику, которая может использоваться для разных целей. Но основное внимание в этой статье будет уделено И вентилю , потому что позже мы будем строить вентиль И , используя схему БЮТ-транзистора .Интересно, правда? Давайте начнем.

И логический вентильЛогический вентиль И представляет собой D-образный логический вентиль с двумя входами и одним единственным выходом, где D-образная форма между входом и выходом представляет собой логическую схему. Связь между входными и выходными значениями может быть объяснена с помощью приведенной ниже таблицы AND Gate Truth Table .

Выходные данные уравнения можно легко объяснить с помощью логического уравнения И логического элемента , которое составляет Q = A x B или Q = AB .Следовательно, для логического элемента И выход HIGH только тогда, когда оба входа HIGH .

ТранзисторТранзистор – это полупроводниковый прибор с тремя выводами, который можно подключить к внешней цепи. Устройство можно использовать как переключатель, а также как усилитель для изменения значений или управления прохождением электрического сигнала.

Для , построенного логическим вентилем И с использованием транзистора , мы будем использовать биполярные транзисторы, которые можно разделить на два типа: PNP и NPN – Транзисторы с биполярным переходом .Символ схемы для каждого из них можно увидеть ниже.

Эта статья объяснит вам, как построить схему логического элемента И на транзисторе. Логика логического элемента И уже объяснена выше, и для построения логического элемента И с использованием транзистора мы будем следовать той же таблице истинности, которая показана выше.

Принципиальная электрическая схема и необходимые компонентыСписок компонентов, необходимых для построения логического элемента И с использованием NPN-транзистора , представлен следующим образом:

- Два транзистора NPN.(Вы также можете использовать транзистор PNP, если он есть)

- Два резистора 10 кОм и один резистор 4-5 кОм.

- Один светодиод (светоизлучающий диод) для проверки выхода.

- Макетная плата.

- A + 5V Электропитание.

- Две кнопки PUSH.

- Провода соединительные.

Схема представляет собой входы A и B для логического элемента И и выход Q, который также имеет питание +5 В на коллекторе первого транзистора, который подключен последовательно ко второму транзистору, а светодиод подключен к эмиттеру. вывод второго транзистора.Входы A и B подключены к базовому выводу транзистора 1 и транзистора 2 соответственно, а выход Q идет к положительному выводу светодиода. На приведенной ниже диаграмме представлена объясненная выше схема для построения логического элемента И с использованием транзистора NPN.

В этом руководстве используются транзисторы BC547 NPN , которые были добавлены со всеми вышеупомянутыми компонентами в схему, как показано ниже.

Если у вас нет с собой кнопок, вы также можете использовать провода в качестве переключателя, добавляя или удаляя их, когда это необходимо (вместо нажатия переключателя).То же самое можно увидеть на видео, где я использовал бы провода в качестве переключателя, подключенного к клемме базы для обоих транзисторов.

Та же самая схема, построенная с использованием вышеупомянутых аппаратных компонентов, схема будет выглядеть примерно так, как на изображении ниже.

Работа и затвор с использованием транзистораЗдесь мы будем использовать транзистор в качестве переключателя, и поэтому, когда напряжение подается через клемму коллектора NPN-транзистора, напряжение достигает эмиттерного перехода только тогда, когда базовый переход имеет подачу напряжения между 0 В и напряжением коллектора.

Точно так же в приведенной выше схеме светодиод будет светиться, то есть на выходе будет 1 (высокий), только когда оба входа имеют 1 (высокий), то есть когда есть напряжение на базовом выводе обоих транзисторов. Это означает, что будет прямолинейный путь тока от VCC (источник питания +5 В) к светодиоду и далее к земле. Во всех остальных случаях выходной сигнал будет 0 (низкий), и светодиод будет выключен. Все это можно объяснить более подробно, разбираясь в каждом конкретном случае по отдельности.

Случай 1: Когда оба входа равны нулю – A = 0 & B = 0 .

Когда оба входа A и B равны 0, в этом случае вам не нужно нажимать какие-либо кнопки. Если вы не используете кнопки, отсоедините провода, соединенные с кнопками и клеммой базы обоих транзисторов. Итак, мы получили оба входа A и B как 0, и теперь нам нужно проверить выход, который также должен быть 0 в соответствии с таблицей истинности логического элемента AND.

Теперь, когда напряжение подается через вывод коллектора транзистора 1, эмиттер не получает никакого ввода, потому что значение вывода базы равно 0. Точно так же эмиттер транзистора 1, который подключен к коллектору транзистора 2, подает питание. нет тока или напряжения, а также значение базовой клеммы транзистора 2 равно 0. Итак, эмиттер транзистора 2 nd выдает значение 0, и в результате светодиод будет выключен.

Случай 2: Когда входы – A = 0 & B = 1 .

Во втором случае, когда входы A = 0 и B = 1, схема имеет первый вход как 0 (низкий), а второй вход как 1 (высокий) на базу транзистора 1 и 2 соответственно. Теперь, когда на коллектор первого транзистора подается напряжение 5 В, фазовый сдвиг транзистора не изменяется, так как на клемме базы 0 вход. Которая передает значение 0 на эмиттер, а эмиттер первого транзистора соединен с коллектором второго транзистора последовательно, поэтому значение 0 переходит в коллектор второго транзистора.

Так вот, второй транзистор имеет высокое значение в базе, поэтому он позволит передать то же значение, полученное в коллекторе, на эмиттер. Но поскольку значение 0 на выводе коллектора второго транзистора, поэтому эмиттер также будет равен 0, и светодиод, подключенный к эмиттеру, не будет светиться.

Случай 3: Когда входы – A = 1 & B = 0 .

Здесь вход 1 (высокий) для первой базы транзистора и низкий для второй базы транзистора.Таким образом, путь тока начнется от источника питания 5 В на коллектор второго транзистора, проходящего через коллектор и эмиттер первого транзистора, поскольку значение клеммы базы для первого транзистора высокое.

Но во втором транзисторе значение клеммы базы равно 0, поэтому ток не проходит от коллектора к эмиттеру второго транзистора, и в результате светодиод все равно будет выключен.

Случай 4: Когда оба входа – один – A = 1 & B = 1 .

Последний случай, и здесь оба входа должны иметь высокий уровень, которые подключены к клеммам базы обоих транзисторов. Это означает, что всякий раз, когда ток или напряжение проходят через коллектор обоих транзисторов, база достигает своего насыщения, а транзистор проводит.

Практически объясняя, когда питание +5 В подается на вывод коллектора транзистора 1, а также вывод базы насыщен, вывод эмиттера будет получать высокий выходной сигнал, поскольку транзистор смещен в прямом направлении.Этот высокий выходной сигнал эмиттера идет напрямую на коллектор 2 транзистора и через последовательное соединение. Теперь, аналогично на втором транзисторе, вход коллектора имеет высокий уровень, и в этом случае контакт базы также высокий, что означает, что второй транзистор также находится в состоянии насыщения, и высокий вход будет проходить от коллектора к эмиттеру. Этот высокий выходной сигнал эмиттера переходит на светодиод, который включает светодиод.

Следовательно, все четыре случая имеют те же входы и выходы, что и фактический логический элемент И.Таким образом, мы построили логический вентиль И с использованием транзистора . Надеюсь, вы поняли руководство и получили удовольствие от изучения чего-то нового. Полную работу установки можно увидеть в видео ниже. В нашем следующем руководстве мы также узнаем, как построить вентиль ИЛИ с использованием транзистора и вентиль НЕ с использованием транзистора . Если у вас есть какие-либо вопросы, оставьте их в разделе комментариев ниже или воспользуйтесь нашим форумом, чтобы задать другие технические вопросы.

Схема затвора CMOS| Логические ворота

До этого момента наш анализ транзисторных логических цепей ограничивался парадигмой проектирования TTL , в которой используются биполярные транзисторы, и общей стратегией, когда плавающие входы эквивалентны «высокому уровню» (подключены к V cc ) входы – и, соответственно, допуск выходных каскадов с «открытым коллектором» – сохраняется.Однако это не единственный способ построить логические ворота.

Полевые транзисторы

Полевые транзисторы, в частности, с изолированным затвором, могут использоваться при проектировании схем затвора. Будучи устройствами с управлением по напряжению, а не по току, IGFET, как правило, позволяют создавать очень простые схемы. Возьмем, к примеру, следующую схему инвертора, построенную с использованием P- и N-канальных IGFET:

Обратите внимание на этикетку «V dd » на положительной клемме источника питания.Эта метка соответствует тому же условию, что и «V cc » в цепях TTL: это постоянное напряжение, приложенное к стоку полевого транзистора по отношению к земле.

Полевые транзисторы в схемах затворов

Низкий вход

Давайте подключим эту схему затвора к источнику питания и входному переключателю и исследуем ее работу. Обратите внимание, что эти транзисторы IGFET относятся к E-типу (режим улучшения), как и устройства , обычно выключенные, .

Требуется приложенное напряжение между затвором и стоком (фактически, между затвором и подложкой) правильной полярности, чтобы сместить их с на .

Верхний транзистор представляет собой P-канальный IGFET. Когда канал (подложка) сделан более положительным, чем затвор (отрицательный затвор по отношению к подложке), канал усиливается, и между истоком и стоком разрешается ток.

Итак, на иллюстрации выше верхний транзистор включен.Нижний транзистор, имеющий нулевое напряжение между затвором и подложкой (истоком), находится в нормальном режиме: выключен, .

Таким образом, действие этих двух транзисторов таково, что выходной вывод схемы затвора имеет надежное соединение с V dd и соединение с очень высоким сопротивлением с землей. Это делает выход «высоким» (1) для «низкого» (0) состояния входа.

Высокий вход

Затем переместим переключатель входа в другое положение и посмотрим, что произойдет:

Теперь нижний транзистор (N-канал) насыщен, потому что он имеет достаточное напряжение правильной полярности, приложенное между затвором и подложкой (каналом), чтобы включить его (положительный на затворе, отрицательный на канале).Верхний транзистор, к которому между затвором и подложкой приложено нулевое напряжение, находится в нормальном режиме: выключен, .

Таким образом, выход этой схемы затвора теперь «низкий» (0). Ясно, что эта схема демонстрирует поведение инвертора или НЕ-затвора.

Дополнительные металлооксидные полупроводники (CMOS)

Использование полевых транзисторов вместо биполярных транзисторов значительно упростило конструкцию затвора инвертора. Обратите внимание, что выход этого затвора никогда не «всплывает», как в случае с простейшей схемой TTL: он имеет естественную конфигурацию «тотемно-полюсный», способный как получать, так и понижать ток нагрузки.

Ключом к элегантному дизайну этой схемы затвора является комплементарный , использующий как P-, так и N-канальные IGFET. Поскольку IGFET более известны как MOSFET ( M etal- O xide- S emiconductor F ield E ffect T ransistor), и в этой схеме используются транзисторы с каналом P и N вместе. , общая классификация схем затвора, подобная этой, – CMOS : C дополнительный M etal O xide S emiconductor.

CMOS Gates: проблемы и решения

КМОП-схемыне страдают из-за присущей полевым транзисторам нелинейности, потому что в качестве цифровых схем их транзисторы всегда работают либо в режиме с насыщением , либо в режиме отсечки , и никогда в режиме с активным . Однако их входы чувствительны к высоким напряжениям, генерируемым источниками электростатического (статического электричества), и даже могут быть активированы в «высокое» (1) или «низкое» (0) состояния источниками паразитного напряжения, если они оставлены плавающими.

По этой причине не рекомендуется разрешать входу логического элемента CMOS плавать ни при каких обстоятельствах. Обратите внимание, что это сильно отличается от поведения логического элемента TTL, где плавающий вход безопасно интерпретировался как «высокий» (1) логический уровень.

Проблемы CMOS с плавающими входами

Это может вызвать проблему, если вход логического элемента CMOS управляется однонаправленным переключателем, где в одном состоянии вход жестко подключен либо к V dd , либо к земле, а в другом состоянии вход плавающий (не подключен ни к чему):

Кроме того, эта проблема возникает, если вход затвора CMOS управляется затвором TTL с открытым коллектором .Поскольку выход такого TTL-затвора плавает, когда он становится «высоким» (1), вход затвора CMOS останется в неопределенном состоянии:

Решение для плавающих входов

Подтягивающие резисторы

К счастью, есть простое решение этой дилеммы, которое часто используется в логических схемах КМОП. Когда для управления входом CMOS используется однонаправленный переключатель (или любой другой тип выхода затвора, неспособный для как источника питания, так и стока ), можно использовать резистор, подключенный либо к V dd , либо к заземлению, чтобы обеспечить стабильный логический уровень для состояния, в котором выход управляющего устройства является плавающим.

Значение этого резистора не критично: обычно достаточно 10 кОм. При использовании для обеспечения «высокого» (1) логического уровня в случае плавающего источника сигнала этот резистор известен как подтягивающий резистор :

Резисторы понижения

Когда такой резистор используется для обеспечения «низкого» (0) логического уровня в случае плавающего источника сигнала, он известен как понижающий резистор . Опять же, значение сопротивления понижающего сопротивления не критично:

.Поскольку выходы TTL с открытым коллектором всегда втягивают, никогда не истощают, ток не подтягивает вверх, резисторы необходимы при сопряжении такого выхода с входом затвора CMOS:

Множественные подтягивающие и понижающие резисторы

Хотя все вентили КМОП, использованные в предыдущих примерах, были инверторами (с одним входом), тот же принцип подтягивающих и понижающих резисторов применяется к логическим элементам КМОП с несколькими входами.Конечно, для каждого входа затвора потребуется отдельный подтягивающий или понижающий резистор:

Это подводит нас к следующему вопросу: как нам разработать вентили CMOS с несколькими входами, такие как AND, NAND, OR и NOR? Неудивительно, что ответ (ы) на этот вопрос показывает простоту конструкции, во многом схожую с конструкцией КМОП-инвертора по сравнению с его эквивалентом TTL.

CMOS NAND Gates

Например, вот схематическая диаграмма для ворот CMOS NAND:

Обратите внимание, как транзисторы Q 1 и Q 3 напоминают последовательно соединенную комплементарную пару из схемы инвертора.Оба управляются одним и тем же входным сигналом (вход A), верхний транзистор отключается, а нижний транзистор включается, когда на входе «высокий» уровень (1), и наоборот.

Обратите также внимание на то, что транзисторы Q 2 и Q 4 аналогичным образом управляются одним и тем же входным сигналом (вход B), и как они также будут демонстрировать одинаковое поведение включения / выключения для тех же логических уровней входа. Верхние транзисторы обеих пар (Q 1 и Q 2 ) имеют выводы истока и стока параллельно, а нижние транзисторы (Q 3 и Q 4 ) соединены последовательно.

Это означает, что выход будет «высоким» (1), если либо верхний транзистор насыщается, и перейдет в «низкий» (0), только если оба нижних транзистора насыщаются.

Поведение схемы CMOS для всех логических входов

Следующая последовательность иллюстраций показывает поведение этого логического элемента И-НЕ для всех четырех возможных уровней входной логики (00, 01, 10 и 11):

CMOS И вентиль

Как и в случае логического элемента И-НЕ ТТЛ, схема логического элемента КМОП-И-НЕ может использоваться в качестве отправной точки для создания логического элемента И.Все, что нужно добавить, это еще один каскад транзисторов для инвертирования выходного сигнала:

CMOS NOR Gates

Схема затвора КМОП ИЛИ-НЕ использует четыре полевых МОП-транзистора, как и затвор И-НЕ, за исключением того, что его транзисторы расположены по-другому. Вместо двух параллельно подключенных транзисторов с источником (верхний), подключенных к V dd , и двух последовательно соединенных транзисторов с понижающим током (нижний), подключенных к земле, затвор ИЛИ-НЕ использует два последовательно соединенных транзистора-источника и два параллельно соединенных транзистора с понижающим током. как это:

Как и в случае затвора И-НЕ, транзисторы Q 1 и Q 3 работают как комплементарная пара, как и транзисторы Q 2 и Q 4 .Каждая пара управляется одним входным сигналом. Если , либо , вход A, или , вход B – «высокий» (1), по крайней мере один из нижних транзисторов (Q 3 или Q 4 ) будет насыщен, что сделает выход «низким» (0 ).

Только в случае на обоих входах будет «низкий уровень» (0), оба нижних транзистора будут в режиме отсечки, а оба верхних транзистора будут насыщены, что является условиями, необходимыми для перехода выхода на «высокий уровень» (1). Это поведение, конечно же, определяет логическую функцию ИЛИ-НЕ.

CMOS ИЛИ Gates

Функция ИЛИ может быть создана из основного логического элемента ИЛИ-НЕ с добавлением инверторного каскада на выходе:

TTL против CMOS: преимущества и недостатки

Поскольку кажется, что любой вентиль, который можно построить с использованием технологии TTL, может быть продублирован в CMOS, почему эти два «семейства» логических схем все еще сосуществуют? Ответ заключается в том, что и TTL, и CMOS имеют свои уникальные преимущества.

В первую очередь в списке сравнений TTL и CMOS стоит вопрос энергопотребления. В этом показателе производительности CMOS является бесспорным победителем. Поскольку комплементарные P- и N-канальные пары MOSFET схемы затвора CMOS (в идеале) никогда не проводят одновременно, ток от источника питания V dd практически отсутствует, за исключением того, какой ток необходимо для подачи тока на нагрузку. TTL, с другой стороны, не может работать без постоянного тока из-за требований смещения биполярных транзисторов, из которых он сделан.

Однако есть нюанс к этому преимуществу. В то время как рассеиваемая мощность затвора TTL остается довольно постоянной независимо от его рабочего состояния (состояний), затвор CMOS рассеивает больше энергии по мере увеличения частоты его входного сигнала (ов). Если вентиль CMOS работает в статическом (неизменном) состоянии, он рассеивает нулевую мощность (в идеале).

Однако схемы затвора CMOS потребляют переходной ток во время каждого переключения выходного состояния с «низкого» на «высокое» и наоборот. Таким образом, чем чаще КМОП-затвор переключает режимы, тем чаще он будет потреблять ток от источника питания V dd , следовательно, больше рассеиваемая мощность на более высоких частотах.

Преимущества CMOS

CMOS-затвор также потребляет намного меньше тока от управляющего выхода затвора, чем затвор TTL, потому что полевые МОП-транзисторы являются устройствами, управляемыми напряжением, а не токами. Это означает, что один вентиль может управлять гораздо большим количеством входов CMOS, чем входов TTL. Мера того, сколько входов затвора может управлять одним выходом затвора, называется разветвлением .

Еще одно преимущество конструкции затвора КМОП по сравнению с TTL – это гораздо более широкий допустимый диапазон напряжений источника питания.В то время как затворы TTL ограничены напряжением источника питания (V cc ) от 4,75 до 5,25 вольт, затворы CMOS обычно могут работать при любом напряжении от 3 до 15 вольт!

Причина этого несоответствия в напряжениях источника питания – соответствующие требования смещения MOSFET по сравнению с транзисторами с биполярным переходом. MOSFET управляются исключительно напряжением затвора (относительно подложки), тогда как BJT – это устройства с управлением по току.

Сопротивление цепи затвора TTL точно рассчитано для правильных токов смещения с учетом регулируемого источника питания 5 В.Любые значительные изменения в этом напряжении источника питания приведут к неправильным токам смещения транзистора, что в свою очередь приведет к ненадежной (непредсказуемой) работе.

Единственное влияние, которое изменения напряжения источника питания оказывают на затвор CMOS, – это определение напряжения «высокого» (1) состояния. Для CMOS-затвора, работающего при напряжении источника питания 15 В (V dd ), входной сигнал должен быть близким к 15 В, чтобы считаться «высоким» (1). Пороговое значение напряжения для «низкого» (0) сигнала остается прежним: около 0 вольт.

Недостатки CMOS

Одним из явных недостатков CMOS является низкая скорость по сравнению с TTL. Входные емкости затвора CMOS намного, намного больше, чем у сопоставимого затвора TTL – из-за использования полевых МОП-транзисторов, а не BJT, – и поэтому затвор CMOS будет медленнее реагировать на переход сигнала (от низкого к высокому или наоборот), чем вентиль TTL, при прочих равных условиях.

Постоянная времени RC, образованная сопротивлениями цепей и входной емкостью затвора, имеет тенденцию препятствовать быстрому нарастанию и спаду цифрового логического уровня, тем самым ухудшая высокочастотные характеристики.

Стратегии борьбы с недостатками

Стратегия минимизации этого неотъемлемого недостатка схемы затвора КМОП заключается в «буферизации» выходного сигнала с помощью дополнительных транзисторных каскадов для увеличения общего коэффициента усиления устройства по напряжению. Это обеспечивает более быстрое изменение выходного напряжения (от высокого к низкому или от низкого к высокому) для входного напряжения, медленно переходящего из одного логического состояния в другое.

Рассмотрим этот пример, «небуферизованный» вентиль ИЛИ по сравнению с «буферизованным», или B-серия , вентиль ИЛИ:

По сути, усовершенствованная конструкция серии B добавляет два инвертора к выходу простой схемы ИЛИ-ИЛИ.Это бесполезно с точки зрения цифровой логики, поскольку два каскадных инвертора просто отменяют:

Однако добавление этих инверторных каскадов в схему действительно служит цели увеличения общего усиления напряжения, делая выход более чувствительным к изменениям входного состояния, работая над преодолением присущей медлительности, вызванной входной емкостью затвора КМОП.

ОБЗОР:

- Логические вентили КМОП сделаны из транзисторов IGFET (MOSFET), а не из транзисторов с биполярным переходом. Входы затвора CMOS

- чувствительны к статическому электричеству. Они могут быть повреждены высоким напряжением и могут принимать любой логический уровень, если оставлены плавающими.

- Pullup и Понижающие резисторы используются для предотвращения плавающего входа затвора CMOS, если он управляется источником сигнала, способным только подавать или отводить ток. Затворы

- CMOS рассеивают гораздо меньше энергии, чем эквивалентные затворы TTL, но их рассеиваемая мощность увеличивается с увеличением частоты сигнала, тогда как рассеяние мощности затвора TTL примерно постоянное в широком диапазоне рабочих условий. Входы затвора КМОП

- потребляют гораздо меньше тока, чем входы ТТЛ, поскольку полевые МОП-транзисторы управляются напряжением, а не током. КМОП вентили

- могут работать в гораздо более широком диапазоне напряжений источника питания, чем TTL: обычно от 3 до 15 вольт против 4,75 до 5,25 вольт для TTL. КМОП вентили

- обычно имеют гораздо более низкую максимальную рабочую частоту, чем вентили ТТЛ, из-за входных емкостей, вызванных вентилями MOSFET.

- КМОП вентили серии B имеют «буферизованные» выходы для увеличения усиления напряжения от входа к выходу, что приводит к более быстрой реакции выхода на изменения входного сигнала.Это помогает преодолеть присущую КМОП-логическим элементам медлительность из-за входной емкости полевого МОП-транзистора и постоянной времени RC-цепочки.

СВЯЗАННЫЕ РАБОЧИЕ ЛИСТЫ: